I’m a simple man. It’s very kind of you to say that you agree with everything I just said, but I hadn’t fully finished my thought. What I was going to say was that I’m a simple man and I like a simple story. Sometimes I finish an interview with someone and—as soon as the video conference call closes—I burst into tears and/or maniacal laughter (figuratively, not literally, you understand… although sometimes it’s been a close call). …

Read More → "Something M-azing This Way Comes"EDA’s acquisition era arrived close on the heels of the EDA era. SDA merged with ECAD to form Cadence in 1987, and the new company’s first acquisition was in 1989. The company has made nearly 40 acquisitions to date. Synopsys incorporated in 1986, and its first acquisition was in 1990. The company has made more than 100 acquisitions to date. Mentor Graphics metamorphosed from a dying CAE company into a vibrant … Read More → "A Brief and Personal History of EDA, Part 5: The Acquisition Era"

My podcast guest this week is Femtosense CEO Sam Fok! Sam and I chat about the role that sparsity will play in the future of AI, the details of Femtosense’s SPU hardware platform and how Femtosense’s AI technology is being used for AI speech enhancement in hearing aids. Also this week, I check out how you can design your own function warp drive with the help of … Read More → "The Future of AI will be Sparse"

As I may have mentioned on occasion, when it comes to quantum computing, one of my favorite quotes comes from the Night Watch tome of Terry Pratchett Discworld series. The quote in question reads as follows: “It’s very hard to talk quantum using a language originally designed to tell other monkeys where the ripe fruit is.” You can’ … Read More → "Affordable Rack-Mount Quantum Computers Are Here!"

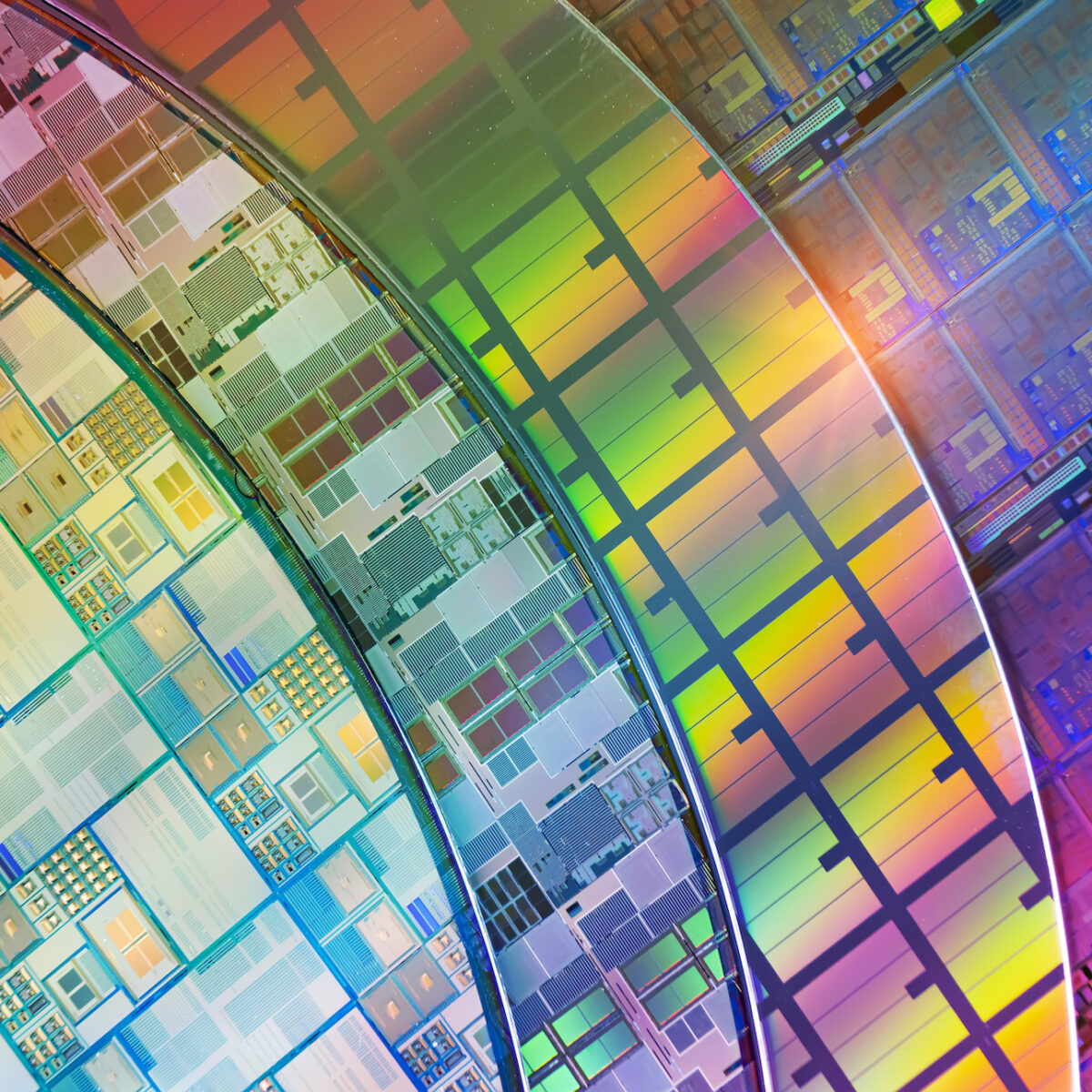

Rising complexity drove the creation of ever-more-powerful tools for electronic design. When circuit board and IC layouts escaped the bounds of pencil, paper, and manual dexterity, CAD tools from Applicon, Calma, and Computervision appeared. When polygon representations no longer sufficed as the first gate arrays appeared, CAE tools from Daisy, Mentor, and Valid appeared. These CAE companies attempted to provide all-in-one design suites for ICs and circuit … Read More → "A Brief and Personal History of EDA, Part 4: Cadence, Synopsys, and Mentor Graphics – The EDA Era"