EDA’s acquisition era arrived close on the heels of the EDA era. SDA merged with ECAD to form Cadence in 1987, and the new company’s first acquisition was in 1989. The company has made nearly 40 acquisitions to date. Synopsys incorporated in 1986, and its first acquisition was in 1990. The company has made more than 100 acquisitions to date. Mentor Graphics metamorphosed from a dying CAE company into a vibrant … Read More → "A Brief and Personal History of EDA, Part 5: The Acquisition Era"

Rising complexity drove the creation of ever-more-powerful tools for electronic design. When circuit board and IC layouts escaped the bounds of pencil, paper, and manual dexterity, CAD tools from Applicon, Calma, and Computervision appeared. When polygon representations no longer sufficed as the first gate arrays appeared, CAE tools from Daisy, Mentor, and Valid appeared. These CAE companies attempted to provide all-in-one design suites for ICs and circuit … Read More → "A Brief and Personal History of EDA, Part 4: Cadence, Synopsys, and Mentor Graphics – The EDA Era"

Are you involved in developing SoCs? Are you banging your head against the wall, desperately trying to determine why you aren’t obtaining the performance promised by the providers of your processor, interconnect, and DDR memory controller IPs? Do I have good news for you? (Spoiler alert. The answer to the last question is a resounding “Yes!”)

In many ways … Read More → "Understanding and Optimizing SoC Hardware Performance"

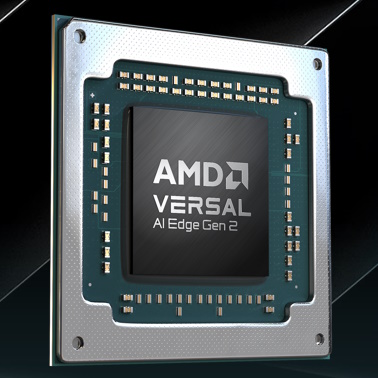

The awesome new AMD devices to which I’ve just been introduced have sparked a trip down memory lane (I know you’re surprised, because I pride myself on my laser-like focus that prevents me from wandering off into the weeds). I remember the 1970s and early 1980s when we thought the simple programmable logic devices (PLDs) of the time were so cool. Those were heady days … Read More → "AMD Rocks with New Versal Gen 2 AI Edge SoC FPGAs"

By the end of the 1970s, the leading CAD companies, including Calma, Applicon, and Computervision had started to lose interest in the electronics market and turned to mechanical CAD. Quite possibly, this lack of interest reflected the demand by electronics and semiconductor companies for something more than efficient drafting systems. The drawings produced by CAD systems were fully capable of producing photomasks for circuit boards and ICs, … Read More → "A Brief and Personal History of EDA, Part 3: Daisy, Valid, and Mentor Graphics – The CAE Era"

My podcast guest this week is MathWorks Space Segment Manager Ossi Saarela and we are chatting all about the intersection of AI and simulation for space applications! We investigate the challenges that engineers are facing today when it comes to the integration of AI into space systems, how simulation can be used to solve these issues, and why the development of more effective AI models for space applications will … Read More → "AI, Simulation and A New Frontier of Space Applications"