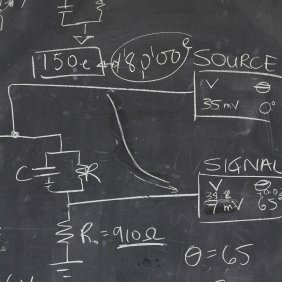

Embedded Signal Processing Capabilities of the LatticeECP3 sysDSP Block

Enhanced DSP Capabilities

The success of the LatticeECP2M family in addressing the 2G/3G wireless arena, coupled with discussions with customers, has served to drive the architectural improvements made in the LatticeECP3 DSP block. Several key points have been addressed. First and foremost, backward compatibility has been maintained with the current LatticeECP2/M DSP. There is also finer control of … Read More → "Embedded Signal Processing Capabilities of the LatticeECP3 sysDSP Block"