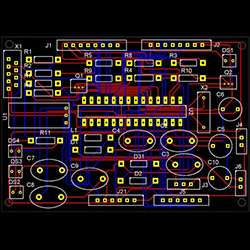

Driving Higher PV Inverter Efficiencies through a Customizable System-on-Chip

With increasing market demands for highly efficient and reliable PV systems, designers are facing many challenges. SoC platforms help designers to deal with such challenges by reducing many of the board-level parasitics and by allowing for more compact, low cost, low power solutions. Microsemi takes SoC to a new level by introducing the world’s first customizable SoC. Microsemi’s SmartFusion cSoC combines a flash FPGA core, a hard ARM Cortex-M3 processor and programmable analog to give integration of control, sensing and power management and communications functions into a … Read More → "Driving Higher PV Inverter Efficiencies through a Customizable System-on-Chip"