Lattice Semiconductor has hit their stride, smoothly executing the strategy they laid out a couple of years ago. In the wake of a failed acquisition, the company turned the page, re-focused, and set a course to make their FPGA technology accessible to a broad range of engineering teams designing high-value applications. It’s a solid strategy – bundling their devices with full-stack solutions including hardware, hardware and software IP, software design and customization tools, reference designs, and design services – everything a typical team would need to quickly get an FPGA-based solution up and running, even with no FPGA expertise on the team.

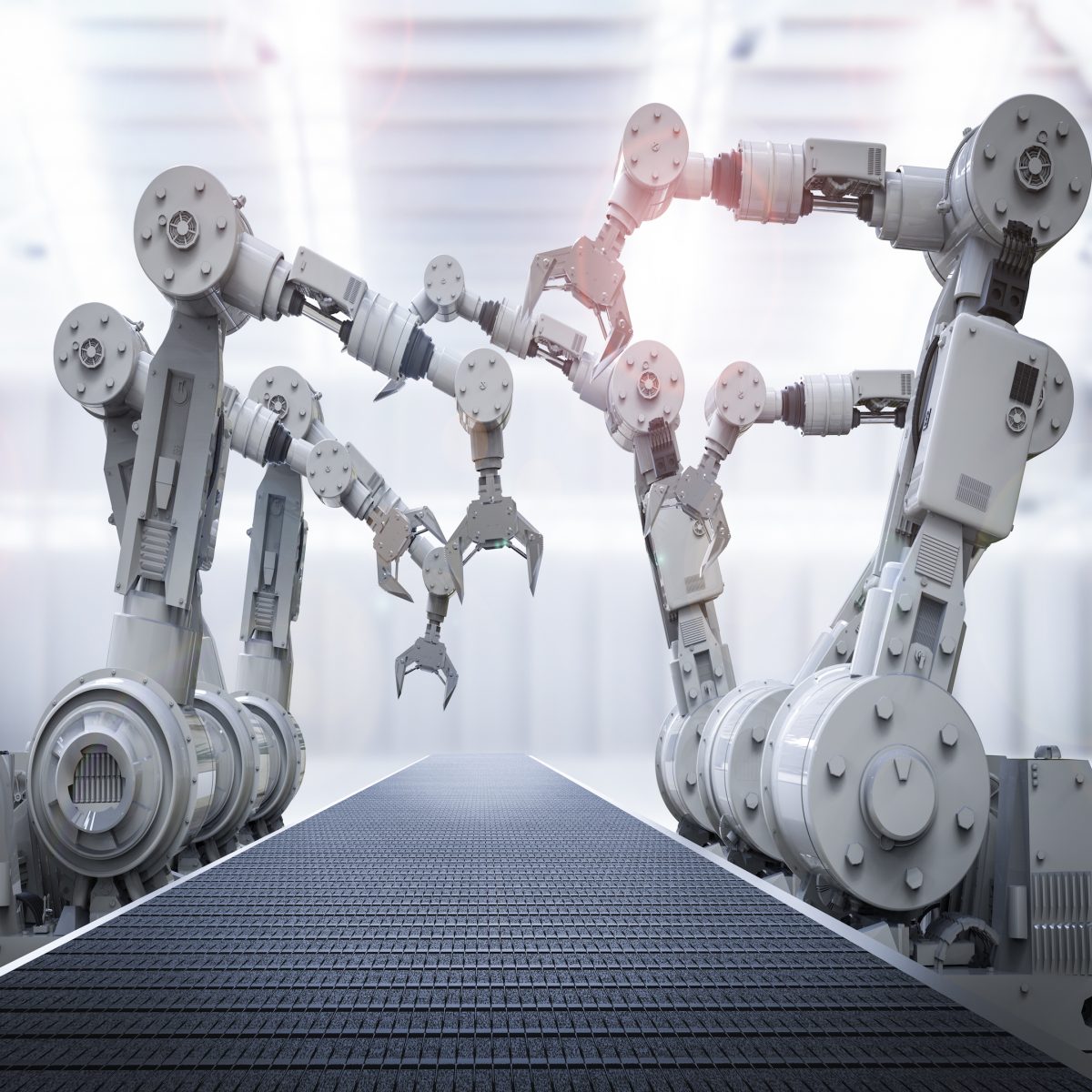

The company has rolled out new solutions at a steady cadence, and the most recent – “Lattice Automate Solution Stack,” is aimed at industrial automation and robotics applications. “Lattice Automate” follows “Lattice sensAI” (for AI inference with sensor data), “Lattice mVision” (for low-power video and embedded vision analytics), and “Lattice Sentry” (for deploying NIST SP800-193-compliant, FPGA-based Platform Firmware Resiliency (PFR) Root of Trust). All of these solutions are configurable to take advantage of multiple Lattice devices from the MachXO3D, Mach-NX, CrossLink-NX, ECP5 / ECP5-5G, and/or iCE40 UltraPlus families.

According to the company, Lattice Automate “provides Industrial Automation system designers with tools needed to evaluate, develop, and deploy FPGA-based, programmable Industrial Automation applications, such as robotics, scalable multi-channel motor control with predictive maintenance, and real-time Industrial Networking.”

This puts Lattice Automate in the arena with a wide range of industrial SoC chips targeted at these same industrial automation applications. The difference, of course, is that Lattice’s solution brings with it the power and flexibility of FPGAs, while getting around the requirement for the engineering team to have FPGA design experts on board. At a high level, this means the solution can minimize power consumption for challenging tasks, provide flexibility in interfaces and application architecture, and can generate significant performance advantages with lower power consumption.

At rollout, Lattice has focused on using the Automate stack for scalable brushless motor control, predictive maintenance, and embedded real-time industrial networking via Ethernet. The hardware layer of the stack takes advantage of the Certus-NX and MachXO3D device families, with RISC-V-based embedded processing systems constructed via the Lattice Propel configuration tool. The combination of the low-power embedded processor with acceleration of key tasks in the FPGA fabric creates a flexible heterogeneous computing platform for edge IIoT systems.

Starting with motor control, a reference system for multi-channel networked motor control with AI-based predictive maintenance has been pre-designed for rapid deployment. Each motor is controlled by a Certus-NX Versa Board, and multiple nodes can be, connected via Lattice’s Ether Connect networking to a controller Versa Board which manages communication with a host PC running the application and monitoring software.

This is a robust example that extends beyond the typical “demo” or “reference design” that often accompanies development kits, and is designed to get at least a generic version of the application up and running in very little time, with no FPGA development required. A GUI-based user interface for system monitoring and control is supplied, and the predictive maintenance capabilities are designed to monitor waveforms from multiple motors with AI-based analysis and fault detection. The Nexus FPGA is used as a central controller, networked via Lattice’s Ether Connect.

There is a lot to unpack there, so let’s start with the underlying FPGA itself. The Certus-NX combines 39K logic cells, 2.9 Mb embedded memory, 56 18 x 18 multipliers, 192 programmable I/O, one lane of 5 Gbps PCIe, two lanes of 1.25 Gbps SGMII (Gigabit Ethernet), two ADCs (each 12-bit, 1 MSPS). The devices are fabricated on 28nm FD-SOI semiconductor process, bringing low power, high performance, and industrial-grade reliability – with particularly robust soft-error resistance. Lattice claims 75% reduction in power consumption vs devices fabricated on bulk CMOS processes. The large RAM blocks and multipliers are tuned for implementation of common AI inference algorithms (such as the predictive maintenance operations mentioned above), and the generous IO configuration gives a lot of options for industrial connectivity.

Lattice plops the Certus-NX down on the Versa Evaluation board using a 256-BGA package. The board provides a PCIe 2.0 endpoint edge connector, two Gigabit Ethernet ports, DDR3L-18661 memory (MT41K64M16TW-107:J from Micron), quad SPI flash (MT25QU128ABA1ESE-0SIT from Micron), three 12-pin Pmod™ connectors for expandability, two camera sensors (one using soft D-PHY interface, and another using parallel interface), multiple clock sources, USB-B connection for device programming and I2C, Four input DIP switches, five push buttons, eight status LEDs and one 7-segment LED. We have written about Certus-NX in detail before.

Lattice Propel provides a set of tools that can implement RISC-V-based embedded processor subsystems in the Certus-NX device, and facilitates creation, analysis, compilation, and debug iof both the hardware design, and the software design for that processor system. Propel includes a drag-and-drop interface for instantiating system components, and facilitates correct-by-construction design. The SDK includes SW/HW debugging capabilities along with software libraries and board support packages. We have also written in more detail about Propel before.

Lattice appears to be thriving as a result of their current strategy. The company says it has tripled its new product introduction cadence and has achieved record financial results. Lattice is expected to unveil the latest member of the Nexus platform – CertusPro™-NX, next month, and their Avant mid-range FPGA platform, in the second half of next year.

It will be interesting to watch Lattice continue to evolve their strategy and deploy new solutions for a variety of markets. By making the transition from component company to solutions supplier, they have expanded their available markets and applications well beyond the traditional FPGA segment, and it seems to be paying off.

One thought on “Lattice Powers-up Industry 4.0”