Are you involved in developing SoCs? Are you banging your head against the wall, desperately trying to determine why you aren’t obtaining the performance promised by the providers of your processor, interconnect, and DDR memory controller IPs? Do I have good news for you? (Spoiler alert. The answer to the last question is a resounding “Yes!”)

In many ways … Read More → "Understanding and Optimizing SoC Hardware Performance"

Like so many of the technologies we take for granted today, I managed to find myself embroiled in the very early days of hardware emulation. This refers to the process of imitating the behavior of one piece of hardware (typically a silicon chip you are in the process of designing) with another piece of hardware (typically a special-purpose emulation system).

… Read More → "A Brave New World of Emulation and Software Prototyping"

I’ve just been introduced to a solution to a computer memory problem I didn’t even know existed. To be honest, I think I was happier not knowing there was a problem in the first place (“Ignorance is bliss,” as the ancient Latin writer, Publilius Syrus sagely suggested).

When I look back, I’ve had a long and involved … Read More → "Rambus’s RAMPART Will Rout Rowhammer"

After seeing what I’ve just seen, you can consider (what I laughingly call) my mind to be well and truly blown. My poor old noggin is now full of ideas, each one triggering a cascade of considerations. Some of these meandering musings may even be germane to what I’m about to reveal. As usual, of course, we will all have to weed through my rambling … Read More → "First Text-to-Speech, Then Text-to-Image, Now Text-to-3D-Animation"

I used to love the title sequence at the beginning of each episode of Star Trek: The Original Series starring William Shatner as Captain James Tiberius Kirk. I’m thinking of the part where the announcer waffled on about the Enterprise’s five-year mission “to boldly go behind the beyond, behind which no man has boldly gone behind, beyond, before” (or words to that effect). … Read More → "AI Boldly Goes Behind the Beyond"

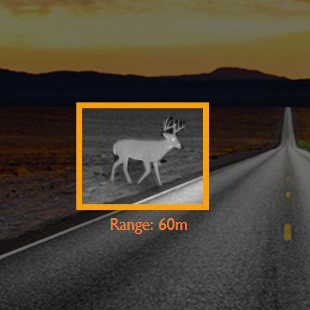

A few evenings ago as I pen these words, my wife (Gina the Gorgeous), your humble narrator (I pride myself on my humility), and a number of other people were visiting at a friend’s house. There were about 20 of us. Only non-alcoholic drinks were consumed. It was dark when we all decided to head for home. Some were walking. I was driving. At least one of … Read More → "Within Five Years, All New Cars Will Be Able to See at Night!"