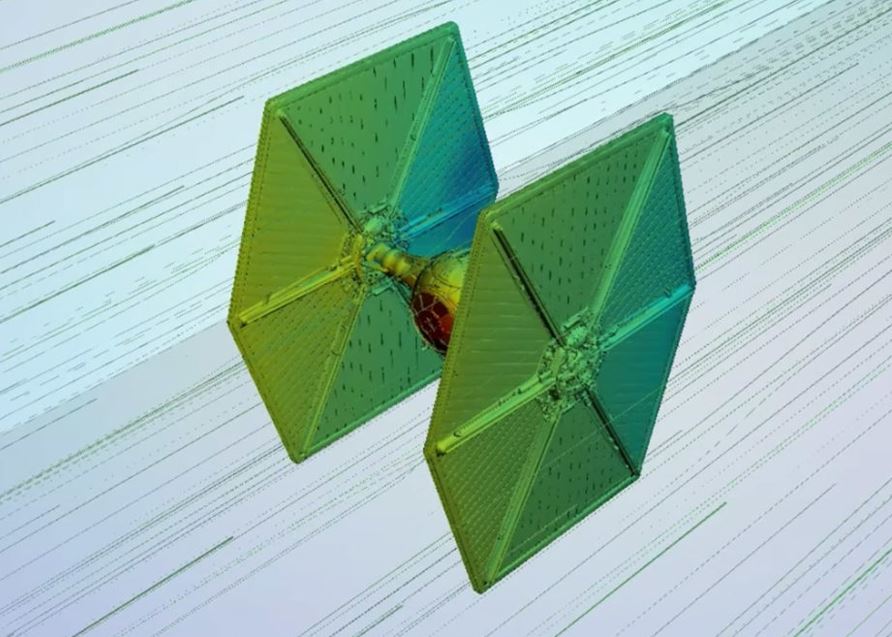

Have you ever wondered how aerodynamic Star Wars ships really are? Well, wonder no more. EC Henry decided to give us some answers. He used AutoDesk’s now discontinued Flow Design software to analyze the aerodynamics and drag coefficients of ships from the Star Wars universe. I know, they don’t travel through air, they travel through space, but it’s still fun to see how aerodynamic their designs are anyhow.

As you may have guessed TIE Fighters are pretty useless when flying through the air. A TIE Interceptor is not much better than a standard TIE Fighter. X-Wings are better, but still not all that great. It turns out that A-Wing fighters are pretty fast. Read more at Technabob.