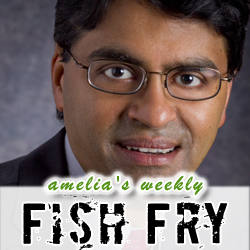

In this week’s Fish Fry, I interview Rajeev Madhavan (Magma CEO) about Magma’s Silicon One initiative, how he thinks Magma fits into the EDA ecosystem and where EDA should be headed in the future. Also, Mentor Graphics plays musical product lines and Catapult C finds itself with a chair….at another company. I’ll give some wild speculation on what actually happened.

I have a DE0-Nano Development Board to give out, but you’ll have to listen to find out how to win.

If you like this new series be sure to drop a comment in the box below.

Fish Fry Links – August 19, 2011

Magma’s Silicon One initiative

Bryon Moyer’s Blog Post: Catapult C Changes Hands

Fish Fry Executive Interviews

John Bruggeman, Former CMO – Cadence Design Systems

Darrin Billerbeck, CEO – Lattice Semiconductor

Lauro Rizzatti, Vice President of Marketing, EVE

Bill Neifert, CTO – Carbon Design Systems

Sean Dart, CEO – Forte Design Systems