Xilinx made a batch of announcements this week aimed at the data center. The company rolled out a new line of programmable network 100Gb/s SmartNIC interface cards, a “SmartWorld AI” video analytics solution, an algorithmic trading framework, and (finally) the Xilinx App Store. Taken together, they make good on Xilinx’s long-term “data center first” strategy. And, viewed on a more macro scale, they represent the execution of a strategy to dramatically grow the FPGA market.

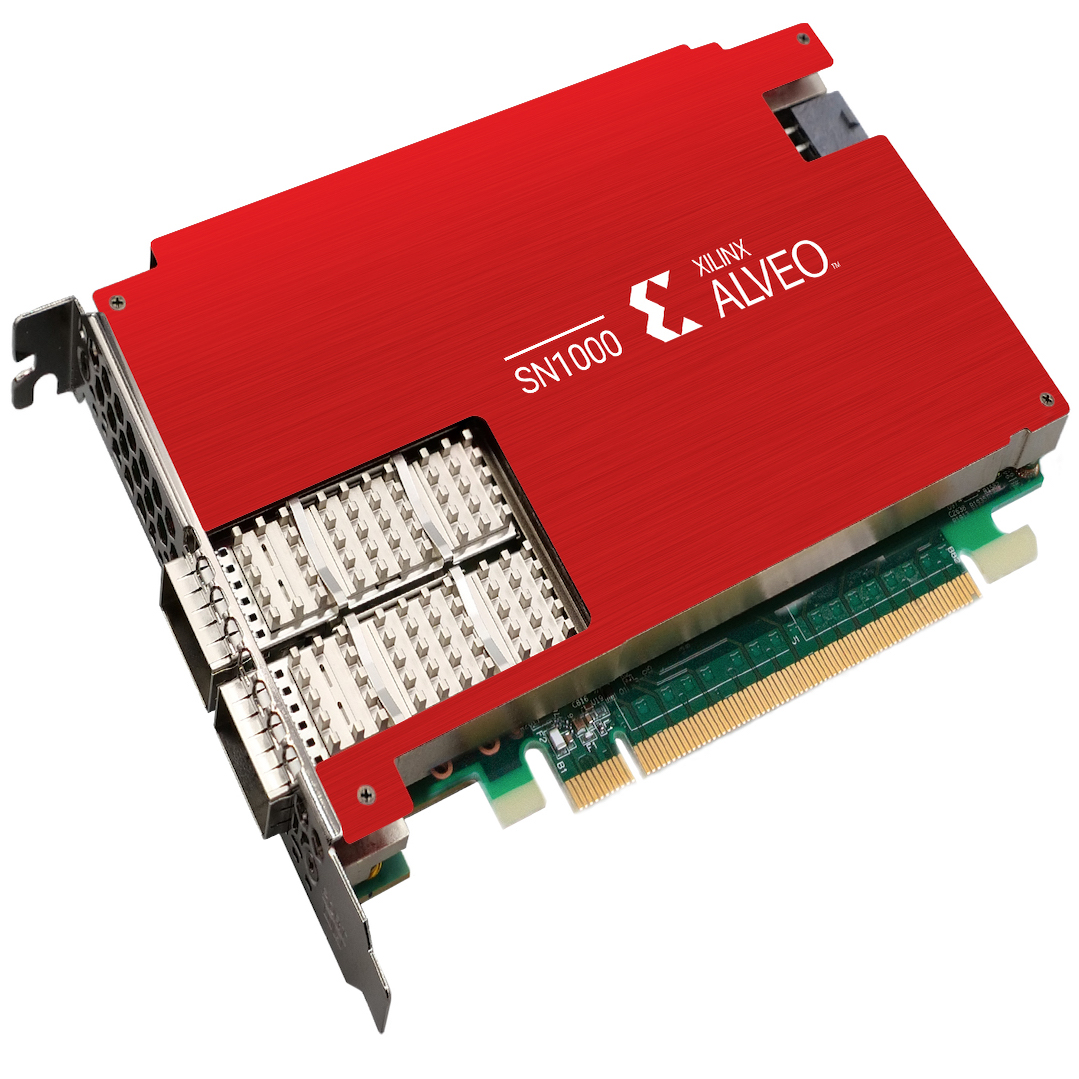

As data rates have skyrocketed, increasing amounts of CPU power have been consumed by networking tasks. The goal of the new SN1000 SmartNIC is to offload those tasks to FPGAs in the network interface card (NIC). The trend toward software-defined networks has given the industry some accepted standards for configuration using P4, C, and C++. Xililnx has piggybacked on those with their Vitis Networking platform to allow software developers to create network functions, protocols, and applications that take advantage of the FPGA acceleration in the SN1000 without having to learn to design the accelerators in the underlying FPGAs. This should enable teams to take advantage of the acceleration capabilities of FPGAs with a zero-friction interface.

This new offering future-proofs the network hardware to a much greater degree, allowing evolution of standards and protocols without the need to replace network cards. The SN1000 opens the door for hardware acceleration for a wide range of networking, security, and storage applications such as Open vSwitch, virtualization acceleration (Virtio.net), IPsec, kTLS, SSL/TLS, Virtio.blk, NVMe over TCP, Ceph, and compression and crypto services.

The SN1000 is based on the Xilinx XCU26 FPGA, which uses the company’s 16nm UltraScale+ FPGA architecture, including a 16-core Arm processor. SN1000 SmartNICs boast dual-QSFP ports for 10/25/100Gb/s connectivity and PCIe Gen 4 interconnect. The SN1000 comes in a full height, half length (FHHL) form factor and works within the standard 75-Watt power envelope.

Moving on to application acceleration, Xilinx announced what they call the “SmartWorld AI” video analytics solution based on their Alveo accelerator card. SmartWorld AI was created in collaboration with a partner ecosystem, and it focuses on latency-sensitive video analytics applications – aiming to deliver deterministic sub-100ms pipeline latency with multiple neural networks on a single card. The solution is powered by the Video Machine-learning Streaming Server (VMSS). Xilinx claims the solution gives the lowest total cost of ownership (TCO) of any currently available solution for this category of latency-sensitive AI video analytics applications.

Smart World ecosystem offerings available as of today include “Smart City” and “Smart Retail” applications from Aupera, which apply Aupera’s existing technology to Xilinx’s Alveo cards. Mipsology provides a toolset for migration of AI applications originally targeted at GPUs to Alveo, as well as plug-and-play high-performance AI inference. And DeepAI delivers AI training at the edge using Alveo accelerators, claiming a 10x performance per cost advantage compared with GPU solutions.

Here again, the goal is to deliver turnkey solutions that do not require the end user to assemble a team of FPGA experts in order to take advantage of the performance improvement, latency reduction, and power consumption benefits of FPGA-based acceleration.

If you’re into high-velocity trading (HVT)–and no, we don’t mean having your broker on speed-dial–you’ll be interested in Xilinx’s new low-latency electronic trading solution. Once again based on Xilinx’s Alveo accelerator cards, the company has added an accelerated algorithmic trading (AAT) extension to the Vitis development environment, giving software developers the ability to quickly create new trading algorithms with sub-microsecond trading performance. This bypasses the usual requirement for a team of hardware engineers to be brought in to implement acceleration based on algorithm changes.

Finally, Xilinx is announcing the FPGA App Store, which does just what you’d expect. The company claims it is the industry’s first FPGA app store, which is somewhat technically true, although there have certainly been marketplaces for FPGA-based design and IP solutions in the past. The FPGA App Store will launch with “ready-to-deploy accelerated applications spanning Smart World AI video analytics to anti-money laundering and live video transcoding.” This long awaited marketplace could be the key to unlocking FPGAs to a much larger market. Imagine if the smartphone had launched with only a hardware platform and a development environment for creating your own applications, but no app store for the average Joe to download ready-to-run apps. Certainly the smartphone market would have grown much more slowly… kinda like the FPGA market has. Xilinx says the apps in the store, developed by Xilinx ecosystem partners, are “containerized pre-built applications that provide an easy way to evaluate, purchase and deploy accelerated applications in minutes.”

Xilinx has been the leading supplier of FPGAs for a couple decades now, and they have tried just about every angle to lift themselves out of the curse of FPGA market mediocrity. The list of tactics employed by FPGA companies to make FPGAs easier to program is long and distinguished. Of course, they have continued to try to make the tools easier to use, but that doesn’t solve the fundamental challenge of understanding HDL code. They have provided extensive libraries of pre-designed IP blocks to make the design process more drag-and-drop, but almost no useful real-world design can be created simply by plugging blocks together. They have introduced HLS tools in an attempt to raise the level of programming abstraction to something that would be reasonable to a software engineer, but HLS tools thus far have proven to be more “power tools” for hardware engineers rather than enablers for software engineers wanting to design hardware or implement hardware acceleration.

On the marketing side, there have been countless efforts to position FPGAs as, well, pretty much anything else besides FPGAs. If you put a processor and an FPGA together and simply call it an “SoC,” will that take the FPGA fear-factor out of designing one? Turns out the answer is no. All the marketing misdirection in the world still results in customers keeping their distance when they realize what is involved in taking advantage of the programmable logic portion of the chip.

The most promising of these strategies is actually shifting from selling components (and associated design software) to selling solutions. If, for example, you need a few thousand network interface cards to plug into servers in your data center, you don’t really need to know that FPGAs are at the heart of the solution, doing the heavy lifting. If the FPGA companies themselves, in collaboration with their strategic partners, can produce complete, turnkey solutions that take advantage of the capabilities of FPGAs without requiring the customer to do any FPGA design work, they could open up vast new markets for their devices.

The challenge with this is that an FPGA company that has for decades made their living by providing chips, tools, and support for engineers doing custom designs has to essentially take over the role of their most successful customers. They, along with ecosystem partners, need to design the final solution using their products, using their in-house expertise on their own technology. Then, at some level, they will end up actually competing against their own long-term customers. The catch is, those customers already have considerable experience selling solutions into those markets that the FPGA company is just trying to cultivate.

It will be interesting to watch as Xilinx attempts this transition from component, tool, and service provider to solutions provider and ecosystem steward.