The Mead-Conway methodology for designing VLSI ICs triggered the development of three dominant CAE companies – Daisy, Mentor Graphics, and Valid – which in turn led to the later development of the three dominant EDA companies – Cadence, Synopsys, and Mentor Graphics. These histories appear in Parts 3 and 4 of this article series. The emergence of the three EDA companies was immediately followed by a long, continuing era of EDA acquisitions, as discussed in Part 5 of this article series.

The Mead-Conway design methodology’s reliance on the use of standard cells also triggered the emergence of design IP starting in the 1990s. One of Lynn Conway’s many contributions to the Mead-Conway design methodology was the concept of using standard cells as fundamental building blocks for IC designs. The use of standard cells started with the ICARUS (Integrated Circuit ARtwork Utility System) design system developed by Jim Rowson for Xerox PARC, but the idea spread quickly throughout the semiconductor industry.

Standard cells are physical designs that are larger than individual transistors. They often implement the equivalent of several logic gates. Initially, every semiconductor device maker and foundry had a proprietary set of standard cells. The designs for these cells and their associated design rules were (and are) treated as trade secrets, so designs were not interchangeable among fabs.

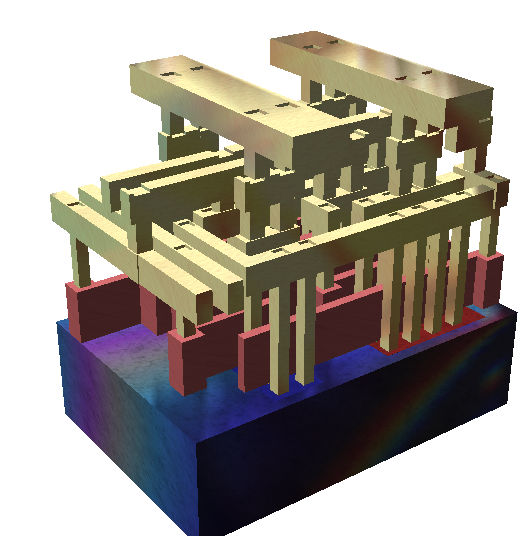

Rendering of a small standard cell with three metal layers, (The dielectric has been removed). Sand-colored structures are metal interconnects, the reddish structures are polysilicon gates, and the multicolored block at the bottom is the bulk crystalline silicon. Image credit: David Carron

Doug Fairbairn, who worked for Lynn Conway at Xerox PARC in the latter part of the 1970s, realized that the Mead-Conway design methodology and its ripple effects on the semiconductor industry needed a newsletter or magazine to disseminate the news and the ideas nucleating around the original concepts. He managed to convince Bert Sutherland, the manager of the Systems Science Lab at Xerox PARC to underwrite the publication of a magazine, to be called “Lambda.” Fairbairn put the first issue together. At Carver Mead’s suggestion, Fairbairn interviewed VLSI Technology, a foundry startup in Los Gatos, California that was developing an ASIC design flow based on the Mead-Conway methodology. That interview became the cover story in the magazine’s first issue. Fairbairn interviewed the company for the article in November and he joined the company the following January, just as the first issue of Lambda magazine went to press.

VLSI Technology was building its own fab to make chips for customers, but the CAE industry hadn’t really gotten up to speed yet, so VLSI Technology needed to develop its own design tools based on the Mead-Conway design methodology. In his oral history, Fairbairn explains:

“…we called it user-designed VLSI. By ’83, there was another term. It was ASIC. The term ASIC got invented in ’83. And so, we were one of those [ASIC] companies. And those were viewed to be… the ASIC companies were viewed to be the companies of the future. And everybody wanted to jump on board. And everybody jumped into the market. I mean Intel even jumped in the market, and Fujitsu, and LSI Logic, and everybody. …meanwhile we had started developing a whole set of design tools because the only thing out there was Calma. And you couldn’t sell a VLSI design story on Calma systems. So, it was understood that we had to develop our own CAD tools because that’s the only way we were going to sell this story.”

Fairbairn hired Jim Rowson, who’d developed the ICARUS design system at Xerox PARC, to head up the CAD group at VLSI Technology. Then things got rolling, as Fairbairn explains:

“…over time, we built the custom – what we were doing became known as – the ASIC business, became known as the cell-based business. Cell libraries. And LSI [Logic] was pushing the gate-array business. And so, we were competing against each other for market share. And we would try to sell people on the cell-based approach. They [LSI Logic] would try to sell people on the gate-array approach. And they had a much better short-medium term strategy in the sense that you could ramp up the designs. You could – they didn’t have to change their methodology much to get people designing gate arrays. Ours was a massive change in methodology. Big training thing. Big risk. They could get people designing gate arrays much more quickly and turn them more quickly as lower cost of entry, lower – it’s an easier sell.

“And so, they were able to ramp revenues faster on their ASIC business than we were able to. We then realized, after a few years, well we really need to be in both. So, we got into the gate-array business. And they realized they needed to be in both. So, they got into cell-based business. So, we both ended up in the same ASIC business fighting each other.

“…What turned out to be valuable was earning – was owning IP. Owning building blocks and owning intellectual property. In the pure ASIC business, you didn’t own any intellectual property.”

By the latter part of the 1980s, VLSI Technology decided to spin out those design tools and its standard cell library into a company called Compass Design Automation. Paul McLellan became the CEO of that new EDA company and inherited VLSI Technology’s standard-cell library. In a Cadence blog, McLellan writes:

“When VLSI Technology spun out Compass Design Automation as a separate company, in addition to all the EDA software, Compass also inherited what we then called the ‘library business.’ We created standard cell libraries (and a few gate-array libraries) not just for VLSI themselves, but also for several other companies, mostly in Asia and Europe. We also created SRAM compilers. Soon after that, Artisan Components was created, so we had the validation of competition that this was a real market. Artisan would eventually be acquired by Arm and transmogrify into what is today Arm’s Physical IP business.”

Eventually, standard cells became larger and larger until they encompassed large LSI blocks such as UARTs. However, the real IP breakthrough was the development of microprocessor IP, starting with Arm. McLellan writes:

“Initially, it was hard for VLSI [Technology] to get customers to use Arm processors in their designs (so that we could build the silicon since initially we were the only licensee). The notion that anyone would license a microprocessor from someone other than an actual semiconductor company that manufactured microprocessors already was too alien. So, the semiconductor world was divided into semiconductor companies that had their own microprocessors (Hitachi, Motorola, NEC, Infineon, NXP, and so on) and everyone else. As chips got larger, ASIC glue logic gave way to true systems-on-chip (SoCs) and these always involved a microprocessor. The companies in the ‘everyone else’ category all licensed Arm as a way to get one.”

The success of Arm microprocessor IP in the ASIC business opened the floodgates for other companies to introduce other microprocessor IP architectures. One of the first to do so was microprocessor maker MIPS, which had been founded in 1984 to commercialize the MIPS RISC processor architecture developed at Stanford University. Silicon Graphics (SGI) based its workstations on MIPS processors and eventually bought the MIPS, which then focused on high-end, workstation-class microprocessors. After more than a decade in the microprocessor chip business, interest in MIPS processors fell off, and SGI spun MIPS back out as an IP licensing company in 1998. In 2013, Imagination Technology bought MIPS and continued to offer MIPS processor core IP. However, the RISC-V processor architecture has eclipsed the MIPS cores (and many other microprocessor architectures). Imagination sold MIPS in 2017. After a series of financial mishaps, MIPS reappeared as an independent company in 2021. Now both MIPS and Imagination offer RISC-V processor cores, alongside more than a dozen competitors in the RISC-V arena.

Two more companies jumped into the processor IP business with configurable cores: ARC International and Tensilica. The idea behind configurable microprocessor cores is that a custom-tailored core can better execute application-specific code, so why not build tools to allow anyone to develop their own microprocessor core? The answer to that question is that very few ASIC designers want to become microprocessor designers. They’d much rather pick a standardized core from a catalog, add it to their design, and be done with it. Consequently, neither ARC nor Tensilica grew as fast as Arm. Virage Logic bought ARC in 2009, and then Synopsys bought Virage in 2010, when the ARC processor IP became part of the Synopsys DesignWare IP series. Cadence bought Tensilica in 2013.

McLellan does a nice job of summarizing the status of semiconductor IP in his blog:

“I expect to see a lot more system-level IP in the future. A lot of IP is only useful when it is bundled with the interfaces, radios, and software required to make it work. These all need to be designed to work cleanly together so that implementing a system in that domain, be it automotive, data center, a 5G base station, or something else, then all the building blocks are available and have been designed holistically.”

IP is now a significant part of the EDA industry. In fact, as a category, it’s now the largest part of the EDA industry. The purchase of ARC and Tensilica by Synopsys and Cadence underscore the intermixing of the IP Era with the EDA industry’s Acquisition Era. Many other IP providers have sprung up, offering DSPs, novel non-volatile memory technologies, and nearly every other sort of technology you might combine into a chip. You’ll find many IP companies in the EDA acquisitions list in the previous article in this series. Startup companies that offered IP of merit (sometimes even if they didn’t), were snapped up and added to the IP libraries of the big EDA companies as yet another dimension to the ongoing competition in the EDA industry.

(Note: During my career, I worked for several IP vendors: Tensilica, Denali Software, and Cadence.)

References

Steve Leibson, A Brief and Personal History of EDA, Part 3: The CAE Era, EEJournal

Steve Leibson, A Brief and Personal History of EDA, Part 4: The EDA Era, EEJournal

Steve Leibson, A Brief and Personal History of EDA, Part 5: The Acquisition Era, EEJournal

Paul McLellan, “A History of Semiconductor IP”, Cadence Breakfast Bytes, February 4, 2021

Oral History of Douglas Fairbairn, Computer History Museum, October 6, 2016