Over the last couple of months, there have been two interesting news items emanating from Mentor Graphics (now officially part of Siemens). They’re largely unrelated to each other, one dealing with system design and the other with IC emulation. We’ll take them in order of announcement.

A System Vision

The first story comes from their SystemVision side of things (one aspect of which we looked at a few years ago). Once a desktop application, it has now migrated into the cloud. Not all features accompanied it on this ascent – and one of the critical missing ones is a price tag. Yup, SystemVision Cloud is free.

This, of course, immediately raises three obvious questions.

The first is, “Where’s the money?” The money comes from component suppliers that want to engage with designers using SystemVision Cloud. They can subscribe to create a private interaction “room” where users can contact them and conduct secure, private conversations with apps engineers and such. Such vendors would presumably have an advantage amongst designers that aren’t completely self-sufficient.

The second question takes note of the fact that Mentor has a pretty good little business going in simulation with their Questa offering. Doesn’t this cut that off at the knees?

The obvious answer to this question is, “No” – because, why would Mentor intentionally do that? The less obvious (but not obscure) reason is that this isn’t for IC design; this is for system design. “But it says you can enter HDL – that sounds like an IC thing.” Yeah, it is an IC thing, but, in this case, it’s assumed you’re going to use standard logic chips (those still exist?) or an FPGA. You can enter the HDL for simulation purposes.

When designing ICs, all hands are on deck to avoid the dreaded expensive mask respin. Not likely they’re going to give you that value for free…

The third question raises the perennial curse on the cloud as a platform for design apps. It’s been tried before, and it has never really gone anywhere. Why? One main reason is concern over security: no one wants to send their family jewels up into the cloud, where they might be hacked. (Never mind the very real possibility that a cloud system may have better security than a private server farm…)

And yet, after all that rejection by designers, here we are again, proposing the cloud for design work. I asked about this, and the response was somewhat surprising. And yeah, a piece of it is generational.

In the software world, cloud tools abound. When Mentor talked to some newer designers that readily use, say, Github, it hadn’t occurred to the designers that these are cloud apps. So much happens in the cloud these days that, for engineers that have grown up this way, that big distinction between local hardware and the cloud is less of a thing. The resistance is gradually easing – especially with these younger designers.

For companies that are still concerned, they can wall off “private” areas of the cloud – presumably eliminating so-called “multi-tenanting,” where more than one company might be using the same box. With a private cloud setup, companies can have more control and more, well, privacy.

This private cloud notion – which maybe should be called a private public cloud – should not be mistaken, however, for what is often referred to as a private cloud: one that uses the purchasing company’s own private server farm to host a cloud – and, within that, a cloud app. This is something that Mentor is not offering.

Strato-spheric

We could sum up the next announcement with a number: 15 billion. As in, gates. That’s a roadmap gauntlet that has been laid down by Mentor’s emulation team for their next-generation Veloce machines. Given that today’s Mentor emulation model number is Veloce 2, the follow-up would naturally be Veloce 3 – ok, no: Veloce Strato. They felt that this edition is different enough to earn a non-incremental name. (“Strato” has no specific meaning.)

15 billion gates is a lot of gates. For perspective, they say that current designs are in the 1.5 – 2 billion-gate range (some of which are multi-chip designs). So they’re setting themselves up for designs in 2022 that are 10 times larger than what they’re seeing today.

So how did these guys wake up one day and decide that they could do 10X the design size? Well, ok, it wasn’t just a momentary crepuscular inspiration. There are three basic enablers: a chip, a connector, and an OS.

You may recall that each of the major emulation companies has a different approach to the root technology. Cadence uses “processors”; Synopsys uses Xilinx FPGAs; and Mentor uses a custom FPGA-like chip (called Crystal). By doing their own FPGA, rather than relying on a commercial version, they have focused on observability – a big deal for debug. This is a requirement that’s specific to emulation, so commercial FPGA makers aren’t likely to go as far in that direction – most other customers would likely not be interested (and wouldn’t want to pay the extra price).

So Mentor gets complete control – both of the logic and the accessibility. They’ve done a few generations of the chip, and this announcement augurs in the latest Crystal version. That’s enabler number 1.

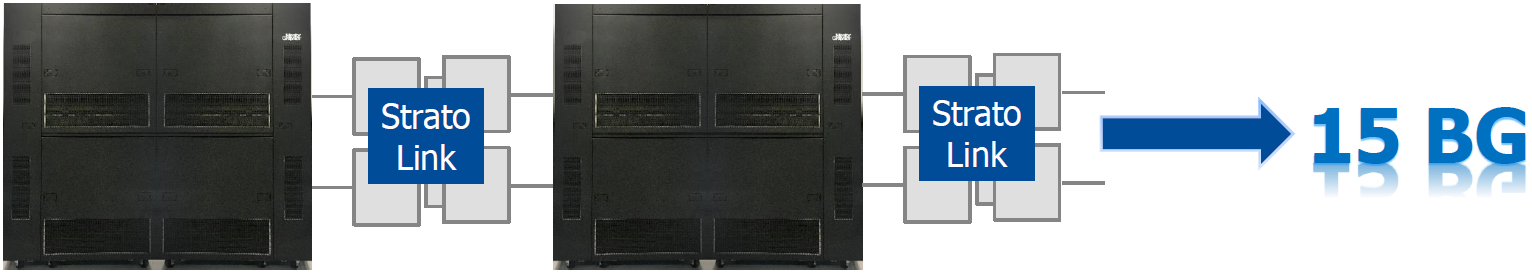

The second enabler is the fabric that allows multiple Veloce Strato boxes to be connected together to emulate a design larger than fits in a single box. The first offering, StratoM, can handle up to 2.5 billion gates. The scale-up to 15 billion isn’t necessarily within the box; it’s the ability to interconnect multiple boxes, and that is done via their new Strato Link interconnect. It’s effectively a very complex switch – which is necessary to handle all of the signals that might need to go between boxes at very high speeds.

(Image courtesy Mentor Graphics)

The third enabler is their latest version of their emulation OS, which they call Veloce Strato OS. It will be a common denominator for all of their emulators and prototyping solutions.

One of the major hitches when scaling up is performance, and the OS and tools have an enormous impact on that. Mentor is saying that, with their latest edition, they’ve sped up throughput by 5 times as compared to Veloce 2. Throughput is something Cadence featured front and center (and takes credit for); Mentor has raised the visibility of it this time as well.

The idea is that productivity is determined by the time it takes to get a design ready to emulate (compilation), then emulate it, and then perform debug to see what needs to change – starting a new cycle. The faster that cycle, the sooner you’ll converge on the correct design. Now, it’s been pointed out before that, from a single compile, it’s common for multiple emulation runs to happen – not just one – before you go back and start changing the design. Nonetheless, the faster all three components are, the better.

Compilation in particular is, they say, 3 times faster than the prior version. The debug side of things, which they call “time to visibility,” has been improved 10 times. They’ve also improved their “co-model” bandwidth by 3X. (For those unfamiliar with co-models, Mentor has a back-door channel that’s much faster than the traditional host-to-emulator channel (SCE-MI 2) for interacting with host-based models.)

All of this is what’s supposed to take them to 15 billion gates. Yeah, there are no designs that big yet (and I recall from experience years ago that trying to fill a device with multiple instantiations of a smaller design to emulate a larger design doesn’t work reliably – Rent’s Rule issues if nothing else). And this is an aggressive, long(ish)-term roadmap, so we’ll see if anything needs tweaking when we get out into that range.

Of course, I also checked in with the two main competitors to see if they had any comment. Synopsys didn’t (which is consistent; they normally don’t comment on competition – at least not officially.) (And no, I don’t have any juicy unofficial sound bites.) Cadence reviewed what they see as the overall Palladium advantages over Veloce – which isn’t really particular to Strato (especially since they presumably haven’t seen an actual Strato box).

Which reinforces the point that this launch is being slow-rolled. You’re not going to find a dedicated Strato page on the Mentor website; they’re cherry-picking lead customers (and even lead industries – networking) as they ramp. So it will bear watching over the next couple of years.

More info:

(No specific Veloce Strato link, other than the press release)

What do you think of Mentor’s cloud-based system design tool? Or, if you’re an IC designer, what do you think about the 15B-gate roadmap?