Somebody said that it couldn’t be done

But he with a chuckle replied

That “maybe it couldn’t,” but he would be one

So he buckled right in with the trace of a grin

On his face. If he worried he hid it.

He started to sing as he tackled the thing

That couldn’t be done, and he did it!

– Edgar Albert Guest (1881-1959)

It is ironic that we more often hear the parody of Edgar Guest’s “inspirational” poem which goes something like:

Everyone said that it couldn’t be done

With a smile, he went right to it.

He tackled the thing that couldn’t be done.

And sure enough, he couldn’t do it.

When it comes to starting new FPGA companies, the parody is much more often the rule than the original. Numerous times over the past decade or so, we’ve been rustled from our sleep to hail the dawn of a new FPGA company… only to watch it waste away and die as the team struggled in vain to conquer the myriad complexities of launching a new, successful product in this challenging arena. For years, there was the specter of patent protection standing guard over the key enabling technologies. With those out of the way, however, the path is no less treacherous. To succeed, a new FPGA company needs a novel silicon architecture, a relationship with a leading foundry partner, expertise and partners in design tools – particularly for synthesis and place-and-route, a stable of basic IP, a savvy marketing team, a solid plan for differentiation, a global distribution channel, partners for fabricating and distributing development kits, a capable AE force, and lots and lots and lots of money. Miss any one of those elements and you are on very shaky ground. Miss two and you’re absolutely doomed.

The problem is, raising investment capital is just the beginning. Compared to the market, those investment guys are easy. The real challenge comes when you work for two or three years to get your first working silicon prototypes back from the fab, and you have your party just at about the same time that both Xilinx and Altera are announcing new families that are now two years ahead of yours. Remember all those stories about how much ASIC design costs? That’s what you’re now facing to spin your new design onto a new process node to try (in vain) to “catch up” to your entrenched, better funded competitors. Your prospects are better going for a jog down the middle of the freeway, at night, in the wrong direction.

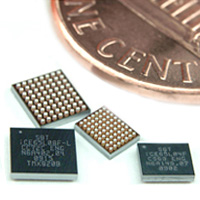

This week, SiliconBlue announced that they are now shipping their new mobileFPGA family in volume to at least ten customers. This is no small feat. Reaching the milestone of volume shipment is way, way down the treacherous path of doom for FPGA startups. In getting to where they are today, SiliconBlue must have passed by the corpses of a dozen or so other FPGA startups littering the road.

SiliconBlue iCE65 (as the name implies) is a low-power, low-cost, small-form-factor FPGA family fabricated on TSMC’s low-power 65nm process. From a process point of view, that puts them exactly at parity with Altera’s just-announced Cyclone IV low-cost FPGA family and ahead of competitive products from Actel and Lattice Semiconductor. The only announced low-cost FPGA at a smaller geometry is Xilinx Spartan-6. Failure mode number one – avoided. They aren’t trying to play catch-up from a weak process position.

iCE65 is cleverly designed as pad-limited. That means that, even if they do have a process node or so deficit at some point, they will be behind on density, but not cost or pin count. Why? As we scale down our devices, one thing that doesn’t shrink at the same rate is IO pads. If you need a certain number of IOs, it’s going to take a certain amount of silicon real estate to ring them around your chip. With smaller geometries, you can cram more goodies into the hole in the middle, but the die itself (and therefore the cost) won’t be getting much smaller. Sure, you can double up the IO rings with staggered bonding, but ultimately you run into limits that are determined by the ability to connect bonding wires, not by the semiconductor process. At present, the only way to get around that limitation is with flip-chip technology, but flip-chip is still (for some odd reason) more expensive than wire bond.

The net result of this pad-limited architecture is that you can guarantee that nobody else can build a chip – any kind of chip (including an ASIC) with the same number of IOs as yours, for less money. Yep, we said “including an ASIC.” So, the only remaining question is – what can you accomplish between those pins? Of course, an ASIC can stuff WAY more gates in there than we can get with FPGA fabric, but many applications don’t need that many gates. At 65nm, it turns out, you can get a decent amount of FPGA fabric inside a pad-limited device – with 4,000 logic cells (4-input LUTs) in a device with 176 IOs and 8000 logic cells in a device of 222 IOs. (OK, SiliconBlue’s marketing folks are obviously industry veterans, because that 4000 logic cells is really 3520, 8000 is really 7680, and they JUST COULDN’T RESIST publishing “system gate” counts of 200K and 400K for those 2 devices. Let’s all get out our “system gate” calculators so we can see that 400,000 system gates is apparently… 7680 4-input LUTs. That’s about 52 system gates for each 4-input LUT. This also means that, since we’re making fun of their marketing – they’re officially a “real” FPGA company.)

SiliconBlue also lists two additional members of the family – 2K LUTs with 128 pins, and 16K LUTs with 384 pins. Oh, and just for the record, the 16K device actually has bodacious 16,896 LUTs. Come on newby marketing dudes! Any self-respecting FPGA marketer would have called that a 20K, or at least a 17K.

So, we have a family that will sell you pins at rock-bottom prices, and will give you enough logic in between them to do a bunch of the things people want to do in mobile devices (about 2-16 times more than you can do in a typical CPLD). What else do we need to succeed in the mobile market? Low power and small form-factor. Let’s take a look at the power picture first. SiliconBlue made their tradeoffs on the “power” side of the power/performance curve with their design. They don’t say specifically what tradeoffs those are, but typically things like gate-oxide width reduce power at the expense of performance. Probably, SiliconBlue turned most of those knobs toward the “low-power” side, and then looked to see if they had enough performance to get by for most mobile applications. It turns out they did. With the power optimizations, the standby current (mostly a function of leakage current) is as low as 8 micro amps. That’s on an SRAM FPGA, boys and girls! Furthermore, the low-power standby state can be reached just by stopping the clock. That’s a lot simpler than many of the power-down dances required in low-power FPGAs.

Finally, we need small form-factor, and this is where the company covered some new ground. SiliconBlue makes their devices available as wafer level chip-scale package (WLCSP) or bare die. WLCSP has a tiny footprint, far smaller than most available FPGA packages. Delivering “known good die” sounds a lot simpler than it is. “Hey, can you just ship those to us without the package please?” Unfortunately, testing, handling, and distribution all get way more complicated without the comfort of plastic packages. Everybody in the supply chain has to be able to handle the KGD process. The advantage, however, is that these die can then be stacked. In many mobile designs, you could drop one of these FPGAs on top of another chip, and the FPGA would then take effectively zero board space. Also keeping the form-factor down is a self-loading option where the configuration is stored in non-volatile configuration memory on the chip itself.

As we mentioned at the onset, there is more than just making good chips required to succeed in the FPGA business. By carefully choosing the mobile market, however, SiliconBlue has avoided some of the stickier areas. Tools, for example, are much less of a concern because we’re dealing with smaller, simpler designs than the behemoth Virtex and Stratix devices. Since we’re not pushing the edge on performance, we don’t need state-of-the-art physical synthesis algorithms and timing-driven optimization pushed to the limits. We can get by with modest, middle-of-the road tool technology just fine.

What does SiliconBlue need to do from this point? Well, they need to keep their funding solid. 10 volume customers probably don’t make them self-sufficient yet, so they need a good pipe back to the funding mother-ship. They need to keep focused on their target market, and not suddenly try to be all FPGAs to all people. They need to ward off the likes of Actel, who is headfirst into the same market space with a different, and differentiated technology – flash-based FPGAs. And, finally, they need to keep a strong distribution and AE network so their prospective customers will have confidence in their ability to deliver. When you’re in the mobile market, the stakes are high, and you want to be sure the chips you design in will be available in the quantities you need, and well supported.

We’re excited to see what happens.