The lease listing on the Pacific American Group’s Web site reads:

“Eight Forty Four East Charleston Road is a historically relevant commercial building in Palo Alto. This building was key in the development of Silicon Valley’s computer business. Here, Robert Noyce and others co-invented the integrated circuit board.”

Well, it’s close anyway.

I don’t really expect commercial real estate agents to fully grok what happened nearly 60 years ago on this site, in this building—not even real estate agents who are leasing historic buildings at Silicon Valley’s ground zero.

A few weeks back, I wrote about 391 San Antonio Road in Mountain View, California, which I called the birthplace of Silicon Valley. (See “391 San Antonio Road: The House that William Shockley Built (and Destroyed).”) My wife and I visited this location, the original and only site of the Shockley Semiconductor Laboratory, just prior to a small celebration of the location’s importance occurred.

Today, on a whim, we decided to visit the birthplace of the first practical, commercial IC. Now before a bunch of Texans get all hot and bothered about the primacy of Jack Kilby’s work on IC development at Texas Instruments, I’m taking nothing away from Dr. Kilby. But Kilby’s work did not lead to the development of a practical IC.

That was the direct consequence of the Traitorous Eight walking out of the Shockley Semiconductor Laboratory in 1957 to found Fairchild Semiconductor. And how far did they walk? Well they set up shop at 844 E. Charleston Road in Palo Alto. According to Google Maps, that’s a distance of just 1.4 miles. Walk down San Antonio Road, hang a left on Charleston, and there you are.

On January 14, 1959, Jean Hoerni showed Robert Noyce the latest version of his groundbreaking planar process for making discrete transistors. Hoerni’s planar process would quickly elevate transistor manufacture from its medieval state of alchemy and artisan-crafted devices to mass production. A little more than a week later, Noyce had extended Hoerni’s idea to encompass a mass-producible integrated circuit and, especially, the lithographically manufactured aluminum interconnect scheme for connecting multiple devices on one chip that truly enabled commercial IC development. The 60th anniversary of that idea is just four months away.

By August, 1959, Noyce had organized a team at Fairchild Semiconductor to make ICs. By May of 1960, Fairchild Semiconductor was making ICs. That’s how fast things went.

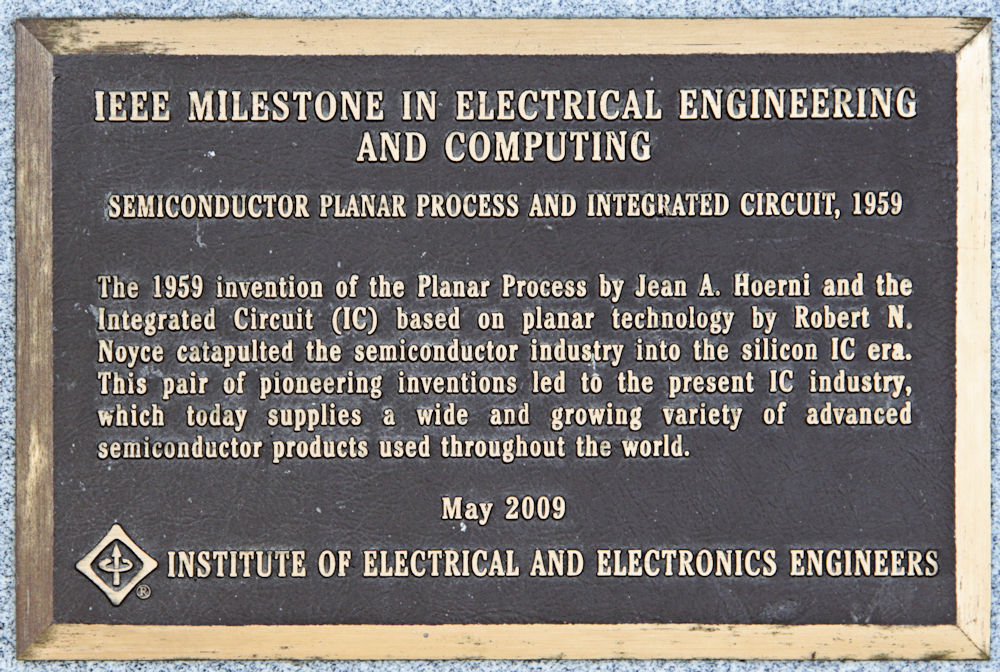

Our visit to 844. E. Charleston Road started with a couple of granite-set plaques commemorating the historic location. One plaque was placed by the state of California. The other’s from the IEEE.

Then, I took a closer look at the building. A lot of historic buildings with true significance to Silicon Valley’s development have either fallen into disrepair or have disappeared into the mists of time. Fairchild Semi’s second location in Mountain View called the Rusty Bucket because of the “patina” on its steel exoskeleton, formerly located at 464 Ellis Street in Mountain View, is one that’s disappeared. It was demolished way back in 1993. Not so with 844 E. Charleston Road.

So how nice can a building with 60 years of history be? Actually, really nice. Today’s visit revealed a building that appears to have been recently refurbished. In fact, it must just have happened because he paint looks brand new and there are a couple of paint buckets still on the overhang above the front door. Peek through the windows and you can see from the front of the building all the way through to the back where there are some large overhead garage doors with glass panels. The first floor’s entirely vacant, with freshly polished concrete floors. Really, the place looks immaculate. (You can see the two commemorative plaques near the front door in the center of the image.)

If you’re into mid-century modern architecture, this place is for you. It’s just ready for a new tenant. Who knows? Perhaps lightning will strike twice. It frequently does around here.

(Photo credits: Steve Leibson)