You may recall that, some months ago, we wrote about SIGFOX. As a quick review, SIGFOX is installing a completely new cellular system optimized for low-data-rate IoT sensors rather than for voice and Youtube. As a French company, they started the build-out in their European neighborhood, but they are supposedly starting their North American build-out now.

Of course, for this to be successful, you have to have devices that can talk to the network. And if the designers of those devices have to cobble together their own discrete circuits or – worse yet – design their own custom SoCs, well, that’s a pretty big barrier.

It would be so much easier if there were a merchant-market chip available that implemented the SIGFOX protocol – both PHY and stack.

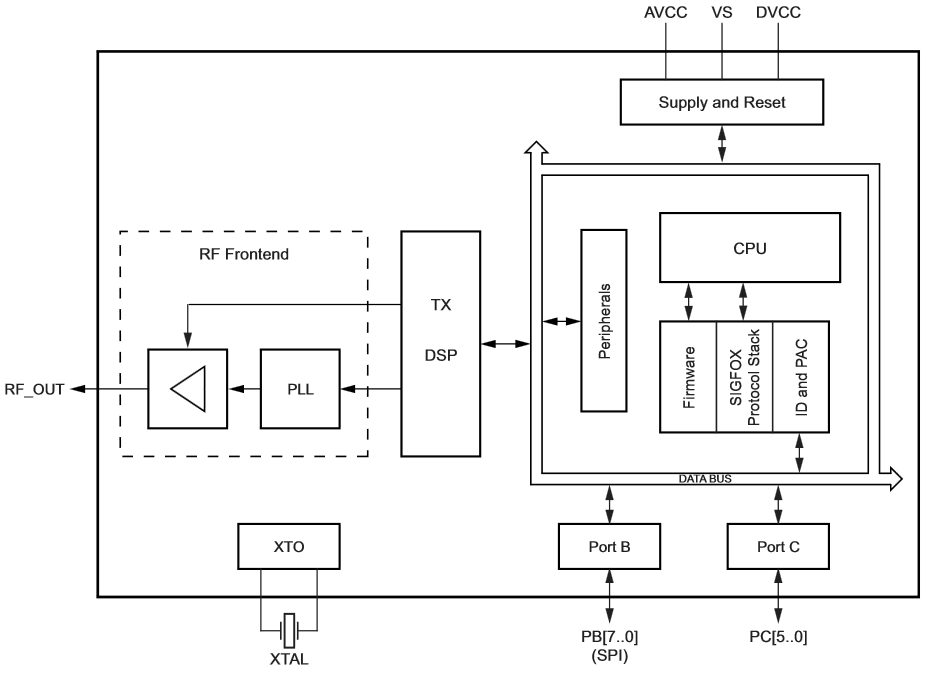

And now there is: Atmel has announced the ATA8520 transmitter – the first SoC to pass SIGFOX’s qualification tests. It consists of the RF block, baseband processing, and an AVR microcontroller for executing the SIGFOX stack and other control functions. Data, as well as other control functions, is entered via an SPI port. The chip has an “OFF” mode that’s not quite off – more like a sleep mode – and reduces current to around 5 nA.

(Image courtesy Atmel)

(Image courtesy Atmel)

The ATA8520 would typically be driven by a system microcontroller or processor; that processor would be freed of any of the details of SIGFOX transmission (traded off for SPI).

Now… all we need is a receiver to listen to all the news being broadcast by the transmitter…

You can read more in their announcement.