Today we looked at the role of Freescale’s new FXLN83xxQ accelerometer for analyzing vibrations. But one feature of the accelerometer had me cocking an eyebrow: analog outputs.

We’ve covered a lot about sensors here before, and in the huge majority of the cases, a sensor consists of a MEMS (or other) sensing element, an ASIC to clean up and digitize the signal, and then a series of registers where all the relevant data gets placed.

An outside entity, like a sensor hub, can then read those registers over a bus connection – typically I2C or SPI. What could be simpler?

Well, I guess an analog output could be simpler: you eliminate all of that messy digital stuff. But it seems to me that, running an analog signal halfway across town to get it to the analog inputs of a microcontroller (aka MCU, or whatever hub is used) would run the risk of seriously degrading the analog value in a way that wouldn’t happen with a digital signal.

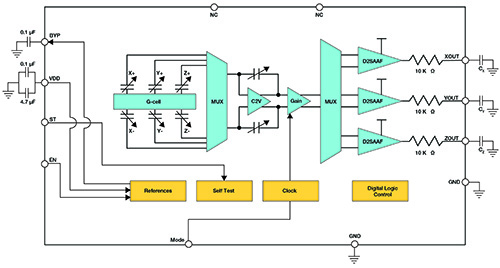

(Click to enlarge)

Image courtesy Freescale.

I asked Freescale about this, and they justify it based on the wide variety of digital interfaces in use, in particular in industrial settings. Heck, they say that even CAN bus is leaving the confines of vehicles and moving into other applications.

Freescale makes lots of microcontrollers. This variety of MCUs partly reflects the diversity of interfaces they may talk to: Rather than having one large unit with all possible interfaces, they offer different devices. And yes, they’re assuming (or at least hoping) that you’ll be using their MCU.

So the idea goes thusly: first off, you simply don’t run the analog signals halfway across town. In these applications, an MCU is likely to be right nearby. (If not, then you want to move it so that it is nearby.) The MCU you choose will then reflect whatever bus you’re using, and that’s where you go digital. They prefer this, obviously, to having to have a bunch of different versions of the sensor to suit the various digital protocols.

There’s one other convenient thing about digital registers, however: they’re good at storing values while the rest of the system goes to sleep for a while to reduce power. Well, apparently these analog outputs can manage the same trick. The internal electronics shut down between samples, but the output is held between samples. This decouples the rate at which the MCU samples the analog outputs from the rate at which the sensor samples the system and allows power as low as 200 µA when running.

That’s how they see it; if you see it differently, then your comments are encouraged below.