SiTime came out with a 32-kHz temperature-compensated MEMS oscillator a few weeks back, targeting the wearables market. 32 kHz is popular because dividing by an easy 215 gives a 1-second period. Looking through the story, there were a couple elements that bore clarification or investigation.

Let’s back up a year or so to when they announced their TempFlat technology. The basic concept is of a MEMS oscillator that, somehow, is naturally compensated against temperature variation without any circuitry required to do explicit compensation.

At the time, they said they could get to 100 ppb (that’s “billion”) uncompensated, and 5 ppb with compensation. (The “ppb” spec represents the complete deviation across the temperature range; a lower number means a flatter response.) This year, they announced their compensated version: They’re effectively taking a 50 ppm (million, not billion) uncompensated part and adding compensation to bring it down to 5 ppm. I was confused.

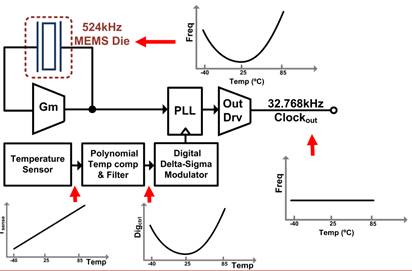

On its face, the compensation is a straightforward deal: take the temperature response of the bare oscillator and reverse it.

Image courtesy SiTime

But what about the “millions” vs. “billions” thing? Why are we compensating within the “millions” regime if they could get to ppb uncompensated?

Turns out, in the original TempFlat release, they were talking about where they think the TempFlat technology can eventually take them – not where their products are now. For now, they need to compensate to get to 5 ppm. In the future, they see doing 100 ppb without compensation, 5 ppb with compensation. That’s a 1000x improvement over today’s specs. Critically, from what they’ve seen published by their competition, they say that they don’t see their competitors being able to do this.

So, in short: ppmillions today, ppbillions later. These are the same guys, by the way, that have also implemented a lifetime warranty on their parts.

There was one other thing I was hoping I’d be able to write more about: how this whole TempFlat thing works. We looked at Sand 9’s and Silicon Labs’ approaches some time back; they both use layered materials with opposing temperature responses to flatten things out. So how does SiTime do it?

Alas, that will remain a mystery for the moment. They’re declining to detail the technology as a competitive defense thing. The less the competition knows…

You can read more about SiTime’s new TCXO in their announcement.