MOUNTAIN VIEW, Calif., Oct. 30, 2018 /PRNewswire/ —

Highlights:

- DesignWare STAR Memory System’s full suite of test, repair, and diagnostic capabilities for embedded MRAM optimize test time without sacrificing test coverage

- New configurable memory BIST and repair algorithms mitigate MRAM defects to enable high test coverage, maximize manufacturing yield, and accelerate ramp to production

- Enhanced design acceleration scripts automate design-for-test functions to reduce integration effort

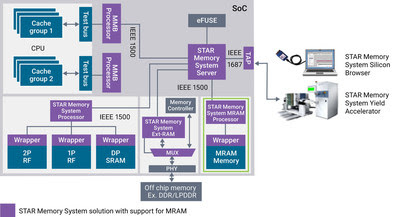

Synopsys, Inc. (Nasdaq: SNPS) today announced that the DesignWare® STAR Memory System™ solution offers new memory built-in self-test (BIST), repair, and diagnostic capabilities for embedded MRAM (eMRAM)-based designs, with initial support for GLOBALFOUNDRIES (GF) eMRAM on the 22FDX® process. The STAR Memory System’s new algorithms target failure mechanisms of embedded MRAM and other types of non-volatile memories during production and in-field test. Support for multiple background patterns and complex addressing modes accelerates automated test equipment (ATE) vector generation, resulting in the highest test coverage for eMRAM, maximized manufacturing yield, and improved system-on-chip (SoC) reliability. In addition, augmented design acceleration capabilities in the STAR Memory System automate the test and repair logic’s planning, generation, insertion, and verification steps for embedded MRAMs to reduce the overall integration effort.

“GF’s eMRAM technology on the 22FDX platform significantly improves power, density, write-speed, and data retention in embedded applications for battery-powered IoT and autonomous vehicle radar SoCs,” said Michael Mendicino, vice president of Product Management at GF. “With the Synopsys DesignWare STAR Memory System and its full suite of post-silicon debug and diagnostic capabilities for embedded MRAM, designers can build greater functionality into their MCUs and SoCs while enhancing performance and power efficiency.”

The DesignWare STAR Memory System is an automated pre- and post-silicon memory test, diagnostic, and repair solution that enables designers to implement high test coverage, reduce design time, lower manufacturing test costs, and maximize manufacturing yield. Synopsys employs rigorous simulation and silicon characterization methods to identify prevalent memory defect mechanisms at every process node for different memory architectures and then develops the test algorithms to detect them. The STAR Memory System solution can test, diagnose, and debug a broad suite of memories including MRAM, SRAM, register file, ROM, CPU/GPU cache, CAM, e-flash, and off-chip memories such as DDR and LPDDR.

“As SoC designers take advantage of the performance, endurance, and technology scaling advantages of embedded MRAM, they will require an integrated test solution to help manage the overall area, power, and yield of their SoCs,” said John Koeter, vice president of marketing for IP at Synopsys. “With the latest enhancements to the DesignWare STAR Memory System, Synopsys is providing the industry with the first commercially available test and repair solution that addresses the specific test coverage needs of eMRAM-based designs, including those targeting GF’s 22FDX process.”

Availability

DesignWare STAR Memory System with MRAM support is scheduled to be available in Q2 2019.

About DesignWare IP

Synopsys is a leading provider of high-quality, silicon-proven IP solutions for SoC designs. The broad DesignWare IP portfolio includes logic libraries, embedded memories, embedded test, analog IP, wired and wireless interface IP, security IP, embedded processors, and subsystems. To accelerate prototyping, software development and integration of IP into SoCs, Synopsys’ IP Accelerated initiative offers IP prototyping kits, IP software development kits and IP subsystems. Synopsys’ extensive investment in IP quality, comprehensive technical support and robust IP development methodology enables designers to reduce integration risk and accelerate time-to-market. For more information on DesignWare IP, visit https://www.synopsys.com/

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the Silicon to Software™ partner for innovative companies developing the electronic products and software applications we rely on every day. As the world’s 15th largest software company, Synopsys has a long history of being a global leader in electronic design automation (EDA) and semiconductor IP and is also growing its leadership in software security and quality solutions. Whether you’re a system-on-chip (SoC) designer creating advanced semiconductors, or a software developer writing applications that require the highest security and quality, Synopsys has the solutions needed to deliver innovative, high-quality, secure products. Learn more at www.synopsys.com.