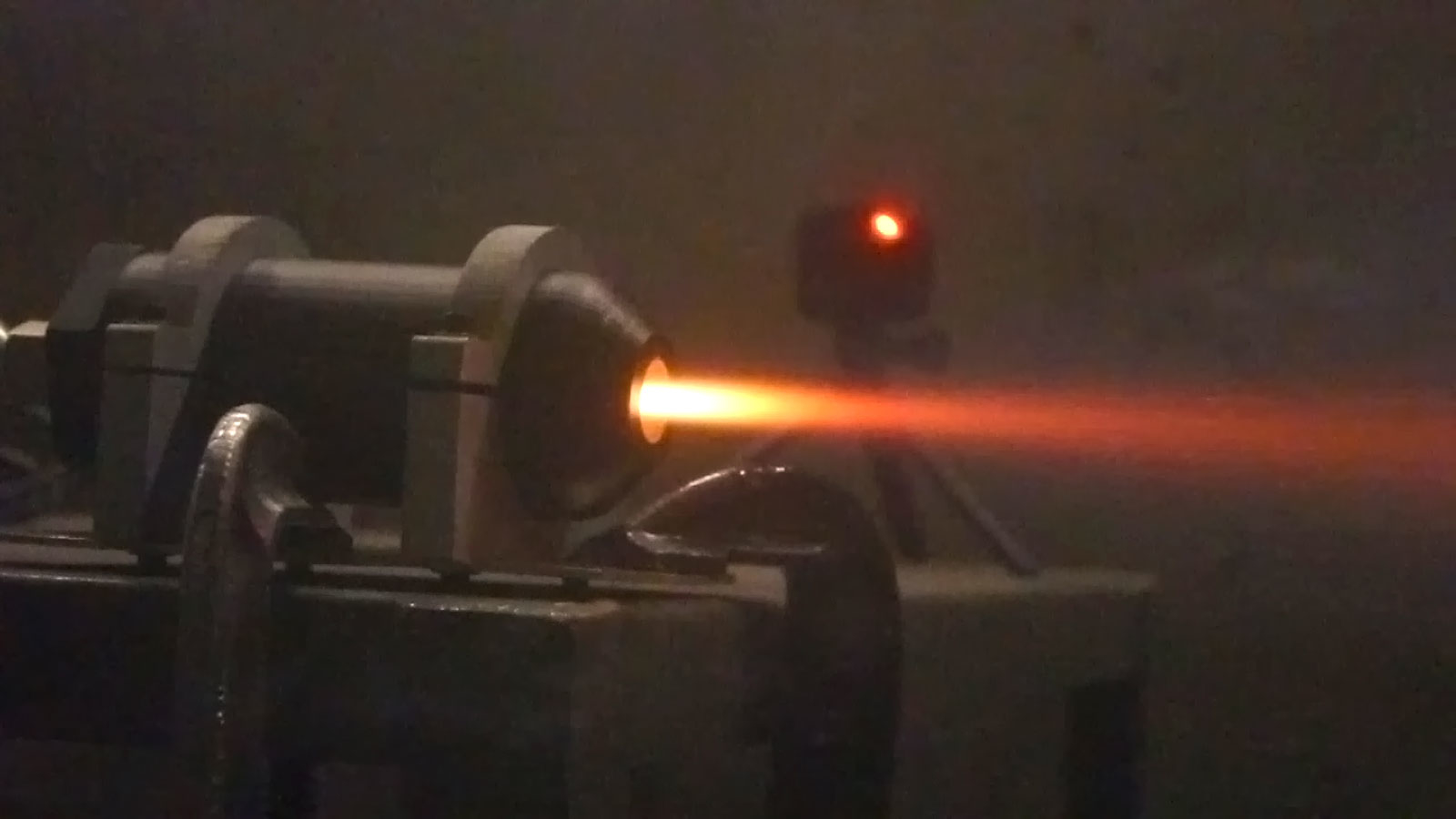

If you’re going to 3D-print rocket parts, you’d want to make them out of metal to handle the stress, right? Not necessarily. MIT has successfully test-fired what it believes is the first completely 3D-printed rocket motor to be made with plastic casing. That’s right — an all too easily melted material was sitting a virtual hair’s breadth away from super-hot propellant. It sounds like a recipe for disaster, but apparently it worked well — it generated real thrust, and there was only a small amount of damage to the motor’s throat after the initial run. A second test didn’t fare so well (it would be useless for moving anything), but MIT hadn’t intended for the motor to fire more than once.

Image: MIT