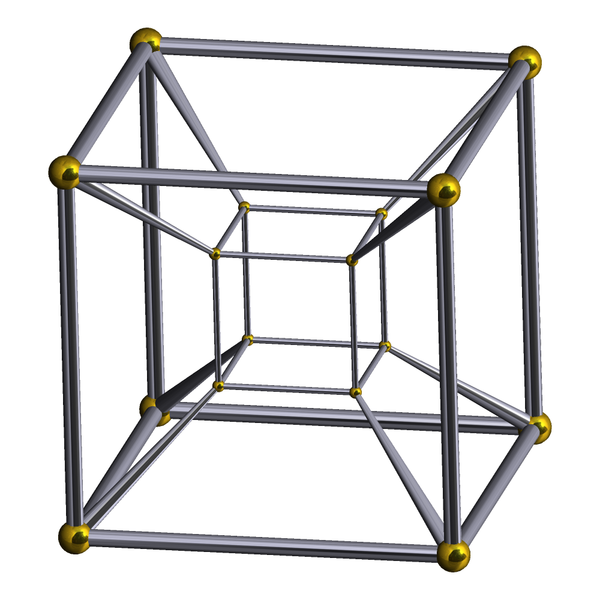

Just when we were trying to digest the recent announcements of 3D FPGA devices, along comes a horizon-widening announcement from TesseracTech of their plans for 4D FPGAs. With companies like Tabula and Tier Logic working to gain a process node or two with their newly announced 3D device architectures, TesseracTech is upping the ante – bringing the first four-dimensional chips to the forefront.

“We’ve known that 3D chips were coming for awhile,” explains Elliott Henthorn, TesseracTech VP of marketing. “Honestly, we knew that three dimensions would never be enough. Xilinx and Altera can usually level the playing field by keeping a couple of process nodes ahead with their 2D technology, and we believe a fourth dimension is required to sustain a real competitive advantage.”

The not-yet-announced TT TetrArray has LUTs arranged in four spacial dimensions. The arrangement has obvious advantages in density. Conventional FPGA architectures use 2D arrays of look-up tables (LUTs) for their programmable fabric. Newly-announced 3D FPGAs take that one step farther (through various means) by giving an effective “stack” of LUTs – allowing much higher effective logic densities. The TetrArray folds the LUT space one more time, giving an exponential advantage in effective device density.

“4D semiconductor technology brings significant benefits to the table,” continues Henthorn. “Obviously we have much greater density, but that’s just the beginning. Take routing, for example. Most IP blocks can be implemented in a single hyperLUT. That means that no routing is required between individual logic elements. Since routing delay is the dominant factor in timing these days, most of our blocks are basically infinitely fast.”

We admit we’re a little confused by that last claim.

We asked for more information on the concept of the hyperLUT. “We have applied for a patent for the underlying mechanism for the hyperLUT, which is what we call Schrodinger’s Latch,” continues Henthorn. “You see, a conventional logic element is either in a zero or one state at any given time. With Schrodinger’s Latch, the logic state is both zero and one until it is observed by an input of another element. We can use this latch to create a LUT that has effectively infinite capacity, creating the exponentially-folded logic space that we get in the TetrArray. Does that make sense?”

In short, no.

TesseracTech is pushing the limits of both physics and credibility with the announcement, which they emphasize is just a technology roadmap – with more details to come as the family gets closer to volume production. However, they are releasing some details about the family in advance. TT TetrArray will not be a family of FPGAs, but rather a single device. “Really, we’ve obsoleted the concept of size in FPGAs,” explains Henthorn. “With 4D density advantages, there’s no point in making a bunch of different devices – all with infinite density. We’re just bringing a single chip to market that will satisfy the needs of everyone.”

While the single device concept makes sense with regard to logic density, we still are not convinced about the one-chip-fits-all concept with regard to IO capabilities. “The TT TetrArray will be available in a wide range of packages,” explains Henthorn. We should be able to give people as many pins as they need for connecting to the outside world. The only trade-off there is package size versus board area.”

The package offering confused us. It seems that if the logic takes basically no space on the device, all the chips would be IO limited, making the chip size a direct function of the number of IOs. “You’re thinking in two dimensions again,” retorts Henthorn. “What you’re saying would be true of conventional wire-bond packaging, or even with flip-chip, although that allows for less constrained IO placement. Our second big breakthrough is applying the concept of Schrodinger’s Latch to IO buffers. You see – since the logic state at any given time is dependent on the observing input, we can connect all the pins of the package to a single pad on the die. This eliminates the space constraint for IO.”

No. No, you can’t.

We were curious what process technology was the basis for TesseracTech’s dubious claims. As far as we are aware, leading semiconductor fabs like TSMC offer mostly conventional CMOS fabrication techniques that don’t seem to lend themselves to the kinds of innovation that TesseracTech is describing. The company is apparently not yet giving out specifics on their fab partners. “If you’ll look at the next PowerPoint slide, you’ll see that our technology doesn’t really depend on a specific fabrication technique. We’ve designed TT TetrArray in a technology-independent fashion so that we aren’t bound by the constraints of conventional IC processes.”

We decided to move the discussion to the design and tool flow for the new product. “For customers that are familiar with traditional FPGA design methodologies, we didn’t want to rock the boat,” says Henthorn. “So, we worked hard to be sure that conventional HDL-based simulation and synthesis methodologies work fine with TetrArray. However, we also didn’t want to scare away new designers who don’t yet know VHDL or Verilog, so we’ve got an alternative flow that requires no tools whatsoever. You can go straight from concept to silicon.”

The company’s ConceptCompiler supposedly takes ideas directly into hardware with no intermediate requirement for hardware description languages. “We’ve exploited the concept of the hyperLUT in our design tool stragety,” drones Henthorn. “If you think about it, conventional design methodologies are focused on getting the right logic values to the right inputs at the right time. However, as I explained with Schrodinger’s Latch, we’ve done away with the concept of logic values at the gate level. Using that idea, and by applying quantum-correlaries of De Morgan’s laws, most designs can be simplified down to a single X. We call that the Solution of Singularity. Working backward from that solution, it doesn’t really matter what logic structure the designer begins with; therefore, we can do away with HDL altogether.

The company says no specific date has yet been announced for availability of TT TetrArray. They are sharing preliminary pricing. “In volume, we plan to ship TT TetrArray at a price of zero,” warbles Henthorn. “We’ve seen price act as a barrier to adoption in many semiconductor startups, and we’re determined to push past that with our launch. By taking cost off the table, you can see that we open the door to much more widespread deployment of the product.”

Clearly, we didn’t hear that right.

We asked whether giving the product away for free would impact the viability of the company from a business perspective. “That’s a really shortsighted view,” replies Henthorn. “If you look at companies like Google, facebook, twitter… all of them gained market share by offering their stuff for free. We’re now taking that concept into the hardware arena. We feel we’ll be able to capitalize on the combination of our technology advantage and a potentially huge installed base to monetize future offerings. We’ve discussed this at length with our equity partner, Chapter 11 Ventures, and they’re completely supportive.”

This isn’t the first time we’ve been a little skeptical on a new FPGA product. A year ago, we ran an article on a new FPGA family from RetroLogik (click here) that hasn’t exactly taken the world by storm. We’re going to reserve judgment on TesseracTech until we see more of their plans in future announcements.

(image courtesy Robert Webb and his Great Stella Software)