San Jose, CA, January 31, 2018 – Movellus, Inc. today announced its flagship products, the Movellus PLL Generator, DLL Generator, and LDO Generator, which expand existing automated digital design and verification tools to deliver the optimized and process-portable IPs in hours, replacing months-long analog design methods. Semiconductor and system companies can use the IP generators to achieve the same precision, performance, and power advantages of the equivalent analog IPs, while fully leveraging the time-to-market and process portability benefits of a true digital implementation.

Creating, Integrating & Verifying Analog Functionality is a Major Design Bottleneck

Today’s high-performance chips include several functions, such as PLLs, DLLs, and LDOs, where the necessary dynamic operation ranges, timing precision, and voltage accuracy have historically only been achievable using analog design methods.

This highly manual analog design process typically takes several months, following which, the IP must still be integrated into the digital design. Any change to the original IP version introduces new potential for errors and additional verification effort. Even purchased IP must be integrated into the design; further, the IP is typically customized for each design.

Because analog-based IP blocks are not directly portable to new process nodes, new IP must be created for every new process. Advanced processes, such as FinFET technologies, make the implementation even more challenging. Due to these factors, custom-designed analog IP blocks can be responsible for the majority of chip failures.

“Analog is still a major design bottleneck, even in predominantly digital chips,” said Muhammad Faisal, President & CEO of Movellus. “Movellus’ PLL, DLL, and LDO generators bring previously custom-designed analog blocks entirely into existing digital flows, improving time to market while also reducing failure risk.”

Movellus PLL/DLL/LDO Generators: New Circuit Architecture & Add-on Software for Digital Design

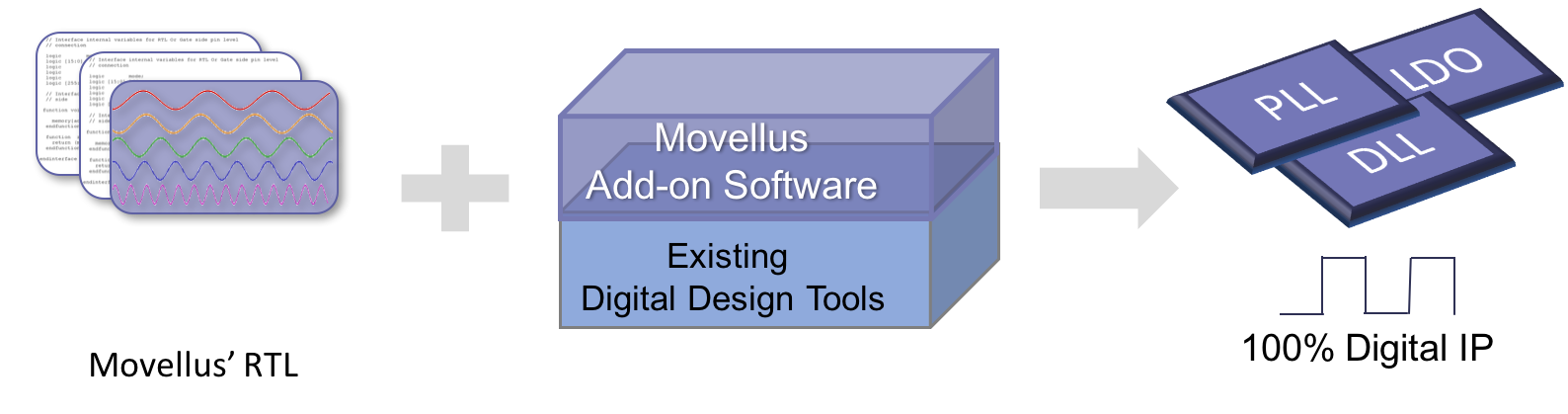

The Movellus IP generators combine proprietary circuit architectures (RTL) with add-on software products that expand digital synthesis, static timing analysis, and place & route tools to create digital implementations of analog functions.

Movellus’ software achieves this result though a combination of factors, such as:

- Enabling existing static timing analysis tools to perform timing verification on analog-type blocks with feedback loops and dynamic operating ranges

Utilizing intelligent constraint iterations to drive existing digital tools to optimize the new circuit elements.

Movellus PLL, DLL & LDO Generators

Movellus PLL, DLL & LDO Generators

Once Movellus’ IP generator software is installed, digital designers can implement Movellus IP in the same manner as with other digital IP. The engineers input their parameters into their existing digital tools using the existing digital user interfaces, then verify the IP utilizing existing RTL simulators.

“Mythic delivers AI that performs hybrid digital/analog calculations inside flash arrays, resulting in orders of magnitude increase in efficiency,” said Dr. David Fick, CTO, Mythic. “The Movellus PLL Generator has unique IP and software technology that expands existing digital tools to enable them to automatically generate PLLs, eliminating manual analog design methods.”

Dr. Fick continued, “Their generator allowed us to focus on designing our SoC without worrying about any schedule slips due to late manual analog customizations needed to meet our goals; for example, when we needed to push a metal stack change, Movellus was able to provide a correct IP in a matter of hours.”

Movellus — Advancing Digital Design with Analog Precision

The IP generated from Movellus’ technology has been silicon proven in process nodes ranging from 130nm to 14nm FinFET. Movellus products advance digital design a major step forward:

1. New PLLs/DLLs/LDOs implemented in hours versus months

By utilizing the automation of digital flows with the precision of analog, development teams save months of development time over manually designing analog blocks, greatly accelerating time-to-market.

Verification time is 20x faster than traditional SPICE methods, with necessary accuracy. Additionally, the software-generated PLLs are “correct-by-construction”, inherently eliminating the errors associated with manual layout of these IPs, saving substantial verification time and resources.

Because the IP blocks use digital models, which are generally available from the foundry sooner than analog model, the need for test chips is reduced.

2. Analog/digital integration overhead is eliminated

Because the new functionality is implemented in same manner as the rest of the digital design and timing flows, any integration overhead is eliminated. Chip level floor planning and timing closure are simplified.

3. Process-portability

The digitally-generated IP has the same easy retargeting as the rest of the digital design.

4. Reduced failure rate

Because Movellus PLLs are implemented digitally, development teams can use standard Design-for-Test technologies. This feature significantly increases the chip level fault coverage and mitigates failure risks, allowing the teams to achieve the same level of predictable reliability as the rest of the digital circuit.

5. What-if analysis & optimization during design

Chip architects can use the Movellus IP generators to do early trade-off analysis for frequency, power and area. Additionally, the generated IP is 4-8X smaller than equivalent analog IP.

Availability

The Movellus PLL Generator and its PLL IP product family are available immediately. The Movellus DLL & LDO Generators and IP products will be commercially available in second half of 2018. The Movellus PLL Generator has term-based software pricing and per-use IP license fees. The PLL IP products have per-use IP license fees.

For more information, visit: www.movellus.com/Analog-Generators-IP and www.movellus.com/IP-products

In other news today, Movellus announced its company launch as a provider of software and IP innovationsthat enable digital design and verification tools to create functionality that has traditionally only been achievable with analog design.

About Movellus

Movellus develops and markets technologies that enable digital design tools to automatically create and implement traditionally analog functionality. Movellus’ flagship products are the Movellus PLL, DLL and LDO Generators, which deliver optimized, process-portable IP in hours. Movellus’ customers include semiconductor and systems companies in the artificial intelligence, networking, and FPGA segments. Movellus is located at 3031 Tisch Way, 110 Plaza West, San Jose, CA 95128. For more information please visit www.movellus.com or call +1 (877) 321-7667.