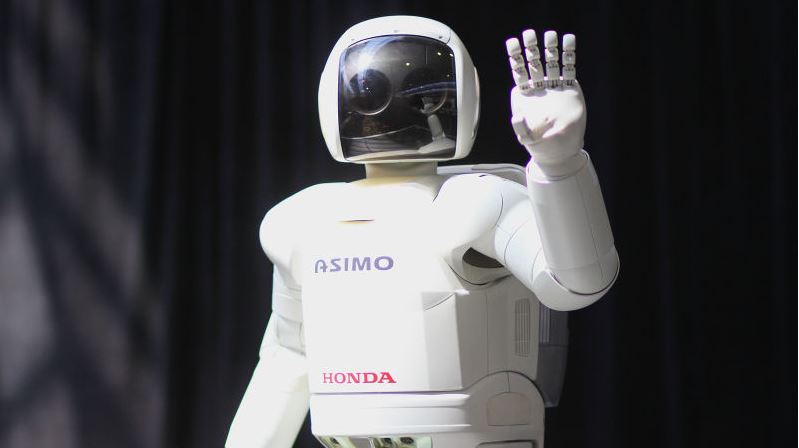

Honda has announced that it will cease development of Asimo, the super cute humanoid that tours the world in the name of stunt marketing. Asimo was 18 years old. Asimo, once heralded as the future of robotics, was not even old enough to buy a beer. But it was always happy to help sell you a Honda automobile.

Don’t get me wrong: Asimo is awesome. The bubble-headed droid has been around as long as the 21st century, and it always felt like a glimpse of the future, when robot assistants would walk to the kitchen and make us cheeseburgers. Sadly, this is a future that will likely never materialize the way that your young mind may have imagined it at the turn of the century. Because Honda, primarily a car and motorcycle company, was never really interested in making Asimo available to the public. Asimo was always a marketing stunt. Honda’s logo was emblazoned across Asimo’s chest and shoulders, like some something out of a NASCAR race. Read more at Gizmodo.