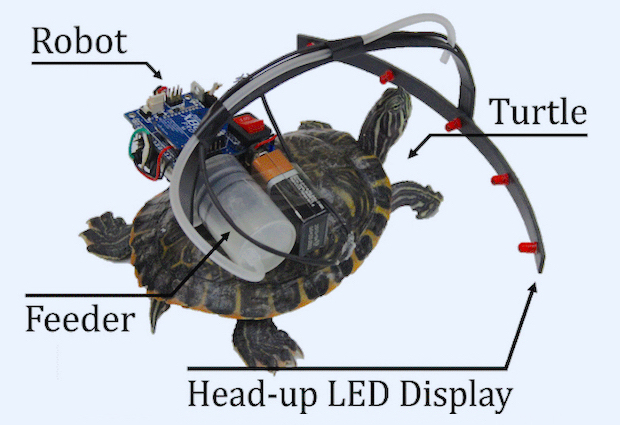

It’s going to be a long, long time before we have amphibious robots that are anywhere near as capable as the mighty and majestic turtle. While many roboticists are working diligently on TurtleBots of all kinds, researchers at the Korea Advanced Institute of Science and Technology (KAIST) have taken things much more literally with the development of a robot-turtle hybrid: a “parasitic robot,” as they call it, that lives on the back of a real turtle, guiding the animal from place to place with the aid of an array of LEDs coupled with positive reinforcement from tasty turtle snacks.

Continue reading at IEEE Spectrum

Image: KAIST