The 2017 winners of the Nobel Prize for Physics were announced today. One half of the prize will go to Ranier Weiss from MIT, while the other half is being awarded jointly to Barry C. Barish and Kip S. Thorne, both from Caltech. The three scientists worked on gravitational wave observation, collaborating between the Laser Interferometer Gravitational-Wave Observatory (LIGO) and Virgo, its European counterpart. The prize was awarded “for decisive contributions to the LIGO detector and the observation of gravitational waves,” according to the Nobel Prize website.

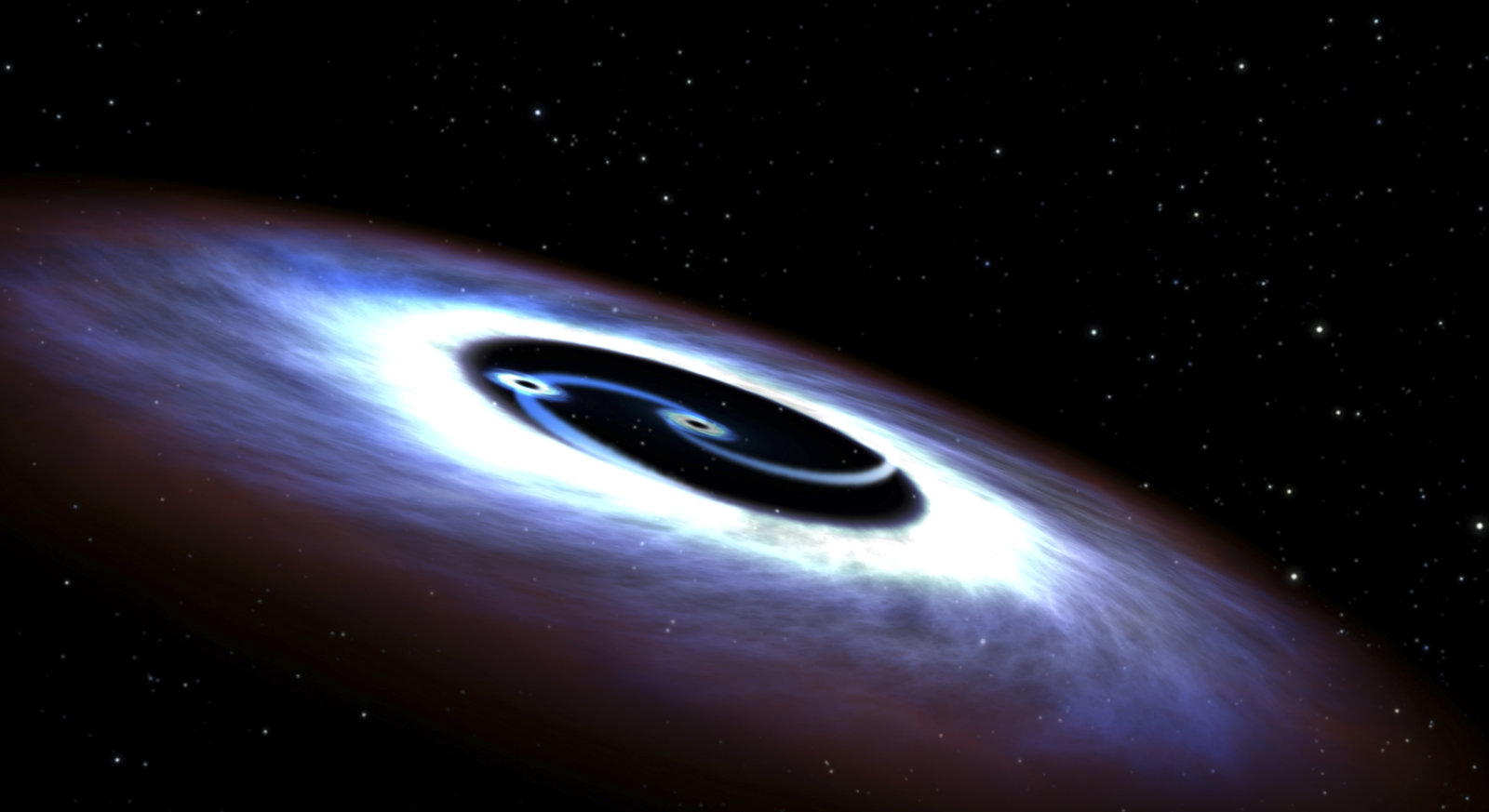

Image: NASA NASA / Reuters