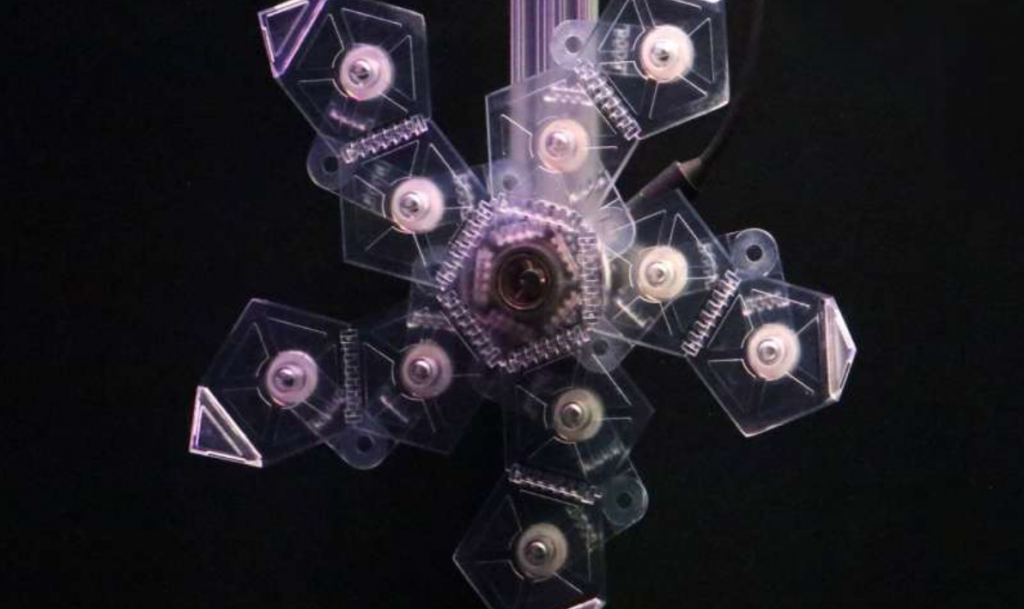

The open ocean is the largest and least explored environment on Earth, estimated to hold up to a million species that have yet to be described. However, many of those organisms are soft-bodied—like jellyfish, squid, and octopuses—and are difficult to capture for study with existing underwater tools, which all too frequently damage or destroy them. Now, a new device developed by researchers at Harvard University’s Wyss Institute, John A. Paulson School of Engineering and Applied Sciences (SEAS), and Radcliffe Institute for Advanced Study safely traps delicate sea creatures inside a folding polyhedral enclosure and lets them go without harm using a novel, origami-inspired design. The research is reported in Science Robotics. Read more at Tech Xplore