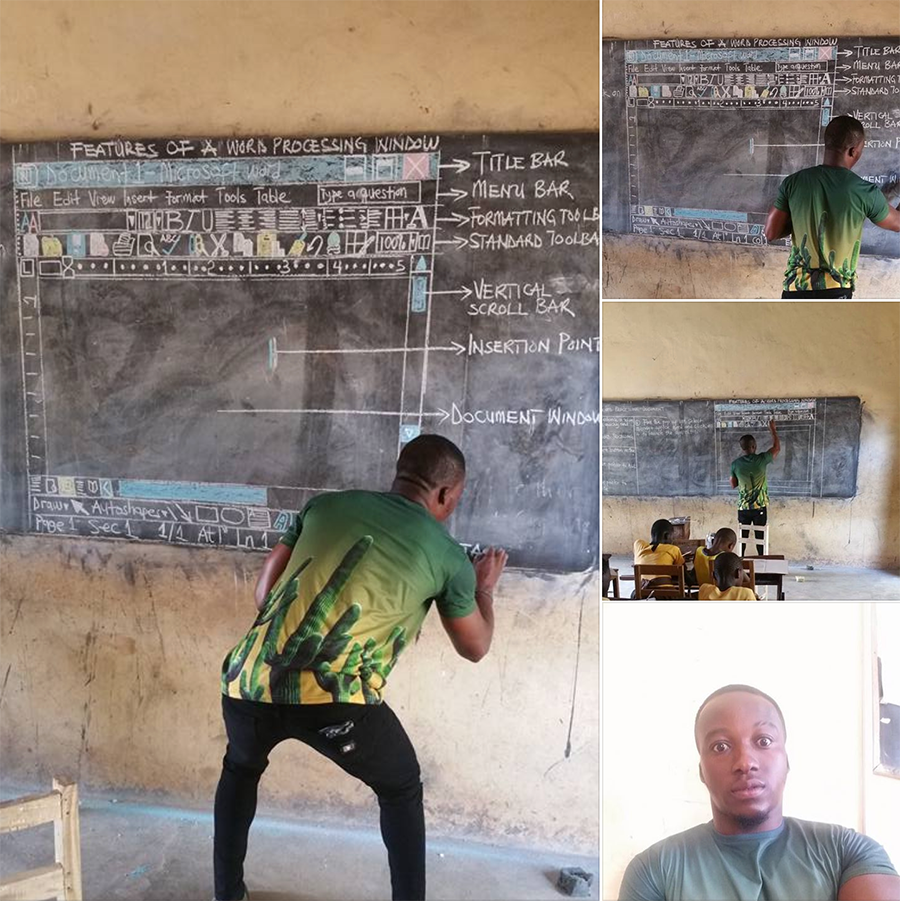

Richard Appiah Akoto is a Ghanaian teacher who faces a pretty discouraging dilemma.

His students need to pass a national exam that includes questions on information and communication technology (ICT) — but the school hasn’t had a computer since 2011.

So Akoto had an ingeniously simple idea: he drew computer features and software on his blackboard, using multicolored chalk.

“I wanted them to know or see how the window will appear if they were to be behind a computer,” Akoto told CNN. “Always wanted them to have interest in the subject so I always do my possible best for them.” Read more on CNN