In Autumn of 1840, Charles Babbage arrived in Turin for a meeting of Italian scientists, where he gave the only public explanation of the workings of his “Analytical Engine.” This machine was the mostly-imaginary upgrade of Babbage’s failed “Difference Engine.”

At the Accademia della Scienze di Torino (which was once run by Babbage’s host in Turin, Prof. Giovanni Plana), they still have all the paperwork that Babbage brought with him to Turin, which Babbage left behind as a gift for Plana and his associates.

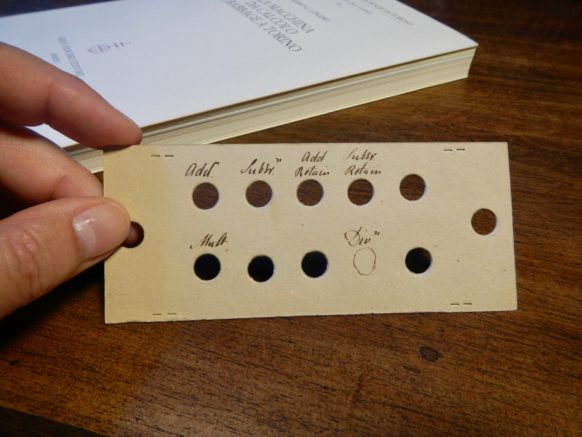

These documents includes charts, engineering plans, lecture notes, a bunch of pencil-scribbled calculations on what seems to be leaves neatly sliced out of Babbage’s own notebooks, and, well, also these punch-cards.