My good friend Adam Taylor recently published a couple of blogs about a new-to-me FPGA vendor named Cologne Chip, a 25-year veteran semiconductor vendor. The company was founded in 1994 as Cologne Chip Designs, and back then, it focused on developing ASICs for the nascent ISDN market. ISDN, or the Integrated Services Digital Network, was the telecom industry’s early effort to develop a digital standard interconnect for telephone systems. Within two years, Cologne Chip Designs had introduced its first ISDN chip. (ISDN standardization took so long that the four-letter abbreviation came to be reinterpreted as “I still don’t know,” “I see dollars now,” or the “innovation that subscribers don’t need.” Eventually, broadband Internet killed ISDN.) Cologne Chip Designs subsequently entered other markets by developing a PCMCIA interface chip and a USB chip. In the year 2000, the company renamed itself Cologne Chip AG and, five years later, expanded into IP design for ASIC development. Cologne Chip introduced its line of small and mid-sized GateMate FPGAs in 2020, but the company had accumulated more than three decades of chip-manufacturing expertise by then.

Like most FPGA vendors except Intel, Cologne Chip is a fabless semiconductor vendor. (Intel’s own fabs make the silicon die for the company’s most advanced FPGAs, while other foundries make the silicon used in Intel’s older FPGAs.) Globalfoundries manufactures Cologne Chip’s FPGAs in a 28nm SLP (Super Low Power) process technology, which makes these FPGAs comparable to AMD’s Spartan 7 and Artix 7 FPGAs and Intel’s Cyclone V FPGAs.

The fundamental logic cell in a Cologne Chip GateMate FPGA is a CPE (Cologne Programmable Element), which can be field-configured as one 8-input lookup table (LUT), a dual 4-input LUT, a 4-input multiplexer, a cascadable 1- or 2-bit full adder, or a cascadable 2×2-bit multiplier. Each CPE also contains two flip-flops. The GateMate FPGA fabric also incorporates dual-ported SRAMs (DPSRAMs), commonly called Block RAMs (BRAMs), which can be configured as one 40-kbit or two 20-kbit RAM blocks. The GateMate FPGAs do not include hardened DSP blocks as do FPGAs from many other FPGA vendors, but you can build DSP blocks using variously configured CPEs.

One other thing you will not find in any GateMate FPGA is a hardened microprocessor core. In that respect, and with the lack of DSP blocks, GateMate FPGA architecture reminds me more of FPGAs from the 20th century than an FPGA from the 21st century, with the caveat that Cologne Chip’s 28nm FPGAs are very much a part of the current century. The lack of hardened processor cores and DSPs is not necessarily a bad thing. Many designers prefer to use “pure” FPGAs – incorporating only programmable logic – in their designs.

The GateMate FPGAs also incorporate one or more SerDes transceivers capable of operating at either 2.5 or 5 Gbps. (The documentation isn’t consistent about the SerDes bit rate.) Like most contemporary FPGAs, Cologne Chip’s GateMate FPGAs employ SRAM-based configuration and load their configuration bitstream from an external EEPROM or some other external device at boot time through an SPI or a JTAG port.

Cologne Chip’s GateMate FPGA data sheet lists six family members with 20,480 to 512,000 CPEs, but as far as I can tell from the documentation, the company has only manufactured the smallest two family members with 20,480 CPEs, 64 20-kbit (configurable as 32 40-kbit) BRAMs, and one SerDes transceiver or 40,960 CPEs, 128 BRAMs, and two SerDes transceivers. According to the data sheet, the company may also be in production with the next largest GateMate family member with 81,920 CPEs, 256 BRAMs, and two SerDes transceivers. In today’s FPGA world, these are relatively small FPGAs.

One of the GateMate FPGA’s unique characteristics is its development tool chain, which is largely based on open-source tools such as Yosys open synthesis suite and OpenFPGALoader. Cologne Chip developed a proprietary bitstream generator, which is consistent with other FPGA vendors, because FPGA vendors are loath to reveal the routing structures and other secrets of their chip designs and open place-and-route tools would bare all. These tools employ a command-line interface. No fancy GUI here.

Cologne Chip provides pre-built, downloadable development tool packages containing binaries for all tools in the chain and sample projects. According to Adam Taylor, these pre-built packages are only 25 Mbytes or so in size, which is much smaller than the multi-Gigabyte tool chain downloads offered by the major FPGA vendors. Discussions of the GateMate tool chain often carry enthusiastic remarks about the “free” development software, but the major commercial FPGA vendors generally offer free editions of their tools for their smaller FPGAs anyway, so I’m at a loss to see much of an advantage in these open tools, other than the obvious religious trappings associated with open-source advocates who might be tempted to gloss over the proprietary, non-open nature of Cologne Chip’s place-and-route tools, which sit at the very heart of the tool chain.

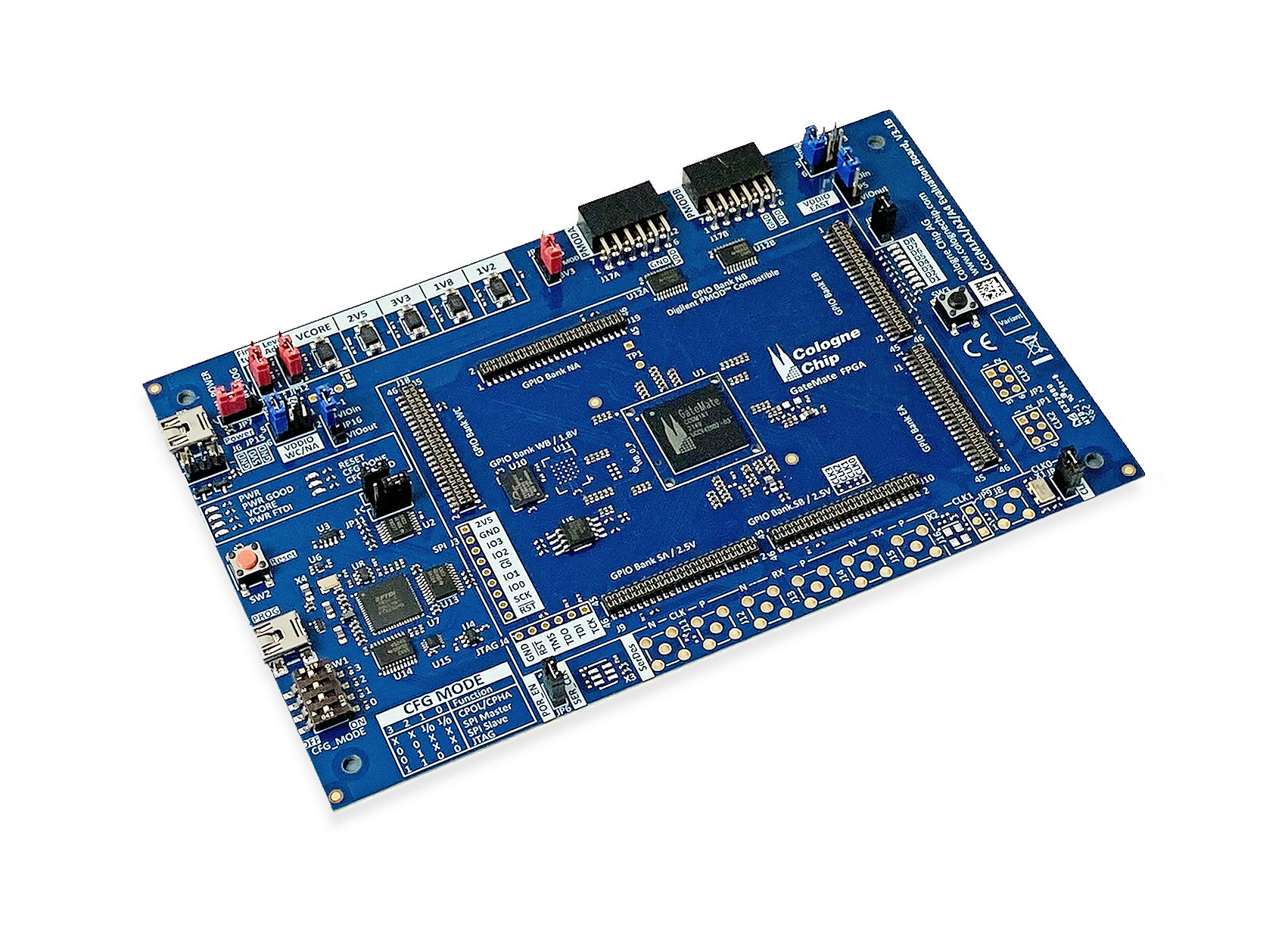

Cologne Chip offers a GateMate Evaluation Board that incorporates a GateMate A1 FPGA, the smallest member of the GateMate FPGA family, with 20,480 CPEs. In addition, the board has USB configuration and power ports, two Pmod ports, an SMA connector carrying the FPGA’s solitary SerDes transceiver port, and 108 GPIO pins on six connectors associated with six of the GateMate A1 FPGA’s eight GPIO banks. Memory on the evaluation board includes a 64-Mbit SPI Flash EEPROM for configuration data and a 64-Mbit HyperRAM chip. In the US, the Cologne Chip GateMate Evaluation Board is available from Digi-Key for $81.25. Just this month, Trenz Electronic announced a low-cost FPGA board incorporating the GateMate A1, and it sells the board, the TEG2000-01-P001, on its Web site for €69.00 plus mandatory VAT. Digi-Key offers GateMate A1 FPGA chips for $21.44 in single-unit quantities, making the FPGA a truly low-cost programmable-logic alternative.

Cologne Chip’s GateMate Evaluation Board costs $81.25 from Digi-Key in the US. Image credit: Cologne Chip

With respect to programmable-logic capacity, GateMate FPGAs are comparable in size and capacity to members of the AMD Spartan 7 and Artix 7, Intel Cyclone V, Lattice Certus-NX, and Microchip IGLOO 2 FPGA families. So why pick Cologne Chip’s GateMate FPGAs over these many FPGA alternatives? I can think of three main reasons. First, Cologne Chip touts the fact that GateMate FPGAs are manufactured in Europe, which could present a tariff-free cost advantage for European systems companies. There’s also some regional pride associated with buying European-made semiconductors, and, in today’s environment, supply chains that stretch into Asia no longer seem as bulletproof as they did when globalism was all the rage.

Second, Cologne Chip’s GateMate Evaluation Board and Trenz Electronic’s GateMate board are truly low-cost FPGA boards. It’s hard to find FPGA development boards costing less than $100 these days, but both of these boards qualify.

Third, the GateMate FPGAs appear to cost less than FPGAs from other vendors, at least in unit quantities when purchased from a distributor. For example, an Intel Cyclone V FPGA with 25,000 logic elements costs $68.92 from Digi-Key in single-unit quantities while the GateMate A1 FPGA costs $21.44 from the same distributor in single-unit quantities. However, unit quantity pricing is rarely representative of negotiated volume pricing deals for production, so caveat emptor (let the buyer beware). Perhaps you can think of additional reasons to pick GateMate FPGAs over the alternatives. If so, please feel free to leave those reasons in the comments below.

In the end, it’s great to see another semiconductor vendor dipping a toe into the FPGA arena. Competition has always been good for the FPGA market. Speaking of which, Intel PSG, the FPGA segment of Intel’s chip business, will be announcing its independence and, presumably, its new name on February 29. I’m sure that the company picked that date, a leap day of a leap month of a leap year, to symbolize the leap back into the FPGA manufacturing pool as an independent semiconductor vendor, separate from Intel, which bought Altera in 2015 and renamed it Intel PSG. After nine years, the FPGA company formerly known as Altera will once more be independent of House Xeon. I wonder what they’ll call the new FPGA company. Any guesses?

References

GateMate and Cologne Chip, Adam Taylor, Adiuvo Engineering

GateMate FPGA Tool Chain, Adam Taylor, Adiuvo Engineering

My guess for the new Intel PSG name is Altera 2.0 .

You are quite clueless for an artcicle author for EEJournal.

1. Re: Toolchain cost. Try using anythign from Lattice that is outside of the free license and tell us about costs.

ALL Lattice free toolchains are:

– “free” only for most basic models that Lattice wants to promote

– even when “free”, license is limited to 1 yr.

– after some time Lattice chenges their focus, new models are introduced and free window moves. If you are stuck with the same board, well, it sucks to be you. Example – i statred with devboard with ECP3. And “free” license. Board was cheap and chip is perfectly fine even now. But license fees are not. And I can’t just pay it one time. It has to be renewed YEARLY. JUst FIY, for Nexus and Avant series they offer Radiant IDE and base fees for it are $2k+ per most basicl licernse YEARLY

– want to have some fun with prehistoric Lattice CPLDs with couple hundred flip.flops ? Or perhaps you want to fix some retro desing or play with a showel of old chips you bought on Aliexpress ? Check the price for Lattice’s prehistoric tools. Even if you manage to run it… YIKES. And it’s ofcourse YEARLY fees.

2. Closed source toolchain issues. Even if you decide to pay it, there are ALWAYS some issues, some differences between yours and production system. And chances are, it will be a showstopper for you and producer won’t care. This is when/where open source shines.

This gets more important with each passing month. You can always take a peek under the hood, fix issues and even keep SW relevant indefinitely. NOT so with closed source. New chips and program versions come out frequently. Once manufacturer looses interest, you are fucked with closed source.

3. You totally overlooked Gatemate’s peculiarities. There has got to be some party trick in those 8-bit LUTs.

Also there is something with that I/Os and SERDES. I/Os can’t do 3,3V. Also chips don’t have HWMULs and they seem RAM starved. But they do have basidc SERDES ( even if presently undocumented) and price is quite friendly, everything considered.

Both you and Taylor seem to have brushed them off to quickly with shallow approach. These things got to have some tricks in their sleeve. I’d say more than one. And it has to be something with that LUT8. I suspect they can do quite fast wide logic with shallow CPE configuration ( since each can be wide) and thuis do quite effective softcores.

IT would be nice to do in-depth article, that is anyone gave a fuck.

Brane212,

1. AMD, Intel, and Lattice offer free tool chains for their low-end devices. All two or three of Cologne Chip’s FPGAs are in that category.

2. The critical parts of Cologne Chip’s tools, the parts that map a design onto the chip, are not open.

3. You’re right, a 1000-word article can’t cover all of the details you’d like. It can’t cover every application of the product being discussed. It can only alert you to something you might want to pursue further. My deepest regrets that this article did not meet your needs, but your existing knowledge of the parts discussed seems to put you far beyond the scope of this introductory article.

AD1: ECP3 are low end devices. Check the licence fees for them.

Same with XO series. Or mature CPLDs. They go from 60-ish to couple hundred flip-flops (ispMACH-V series, still in production). Can’t go cheaper/lower end than that. Now check the licence fees and conditions for SW.

AD2: That might be a shame, but still FAR better than anything competing, especially if its permanently free (as in beer, at least).

I see nine Lattice PLD families that have free software support. Sorry to hear that the specific devices you want are not supported with free software.

Now show me ONE with permanent support – that if you download the particualr SW version, you can be sure to use it as you wish.

ALL I can see are time limited, even if free. So, after a year of use SW stops working, license renewal is needed AND you can well be left as they say, “with your cock in your hands”.

Seems you’d like for me to defend Lattice’s software licensing policies, Mr. Brane. No thanks. You got a beef with Lattice? You handle it. Conversation over.

Note that the nextpnr project provides (free and open source) support for ECP5, MachXO2/XO3, and Nexus series. For the most part you don’t have to interact with any Lattice tools at all, although there are limitations on which timing constraints can be used.

… “free and opensource” sounds nice and dandy. Yet, the as-is nextpnr is hardly timing aware, yet alone timing driven. Yosys is rather thin when it comes to digesting modern System Verilog, and without serious plans to gaining weight in that segment. Even more importantly, Yosys may surprise you even to this day by generating netlists that don’t match the RTL:

– https://github.com/YosysHQ/yosys/issues/4457

Even Cologne proprietary PNR has room to mature:

– https://github.com/chili-chips-ba/openCologne/issues/17#issuecomment-2172082772

As you naturally first doubt your design, it takes time to get to the root of the bugs of this nature. Then, you’ve got to wait for the volunteers to fix them. Time is money. As Steven’s wisdom goes, “caveat emptor”, esp. if you are bound by commercial contracts that oblige you to pay fines for not delivering design they paid you for…