Part 1 of this article describes how Busicom chose Intel to develop and manufacture the world’s first commercial microprocessor. Part 2 describes how the Intel 4004 microprocessor was created and brought to market.

It was late March or early April in 1970, and Busicom’s Masatoshi Shima was very angry! He’d visited Intel with Busicom executives several times in 1969, and Busicom had agreed to pay Intel a development fee to design and manufacture a proprietary 4-chip set for Busicom’s modular 141-PF calculator. Shima had developed an initial design proposal that called for a dozen large LSI chips, which Intel simply could not manufacture or package. Intel’s Ted Hoff then developed an architectural proposal that called for a chipset – including a 4-bit CPU, RAM, and ROM – to be called the MCS-4. Busicom execs had chosen Hoff’s proposal. After the agreement was made, Shima returned to Japan and further refined plans for a desktop calculator based on Hoff’s proposed chipset. He also wrote several firmware programs, which helped him debug the proposed CPU instruction set.

It almost didn’t happen, Round 2

Shima returned to Intel on April 7, 1971 and found that no progress had been made on developing the MCS-4 chipset during the intervening months. Worse, when he arrived, he found that Ted Hoff was now working on a completely different project. (A project that produced the first 8-bit microprocessor, the Intel 8008.) That left Federico Faggin, who’d joined Intel just a week before Shima arrived from Japan, to work on the MCS-4 project.

Shima asked to see the schematics for the chips in the set. Faggin informed Shima that he’d only been working at Intel for a week and, by the way, there were no schematics for any of the MCS-4 chips. No one had worked on the project.

Here’s how Faggin describes the situation:

“I was hired to be the project leader for the “Busicom project.” In 1969, Busicom had developed the design for a family of calculators and they wanted Intel to transfer their design into silicon. Their design was a special-purpose, CPU-based machine with macro-instructions, ROM, and shift-register read-write memory, partitioned in 7 different chips. The CPU function was distributed onto three separate chips. When Ted Hoff saw the Busicom design, he was surprised by its complexity and proposed a simplified architecture based on a more general-purpose, single-chip, 4-bit CPU, and separate chips for ROM with I/O, RAM with I/O, and shift register. After the basic architecture and specification of this four-chip set, called MCS-4, was completed, the project was transferred to the MOS Design group for implementation.

“For a typical custom design, the customer usually provided a verified logic design to the MOS vendor for implementation in silicon. The semiconductor company would then translate the customer’s logic design into appropriate MOS circuits, do the chip layout, create the masks, the customized testing software, and finally produce the chips for the customer. Companies doing MOS custom chips over a number of years had developed a design methodology and a number of pre-characterized circuit building blocks to aid in error-free and rapid chip development.

“The original design that Busicom wanted Intel to translate into seven custom chips was accordingly already designed, and it was built and verified to be correct at the logic gate level. Hoff’s proposal, however, was only conceptual and no logic design or verification had been done. Since Intel was dedicated to memory chip design, it had no experience with random logic chip design; it had no design methodology and no pre-characterized circuit building blocks.

“Furthermore, the style of design required with silicon gate technology was quite different than random logic with metal gate, for which methodologies already existed. The characterization and production testing required testers and testing methods that Intel also didn’t have. The day I joined Intel, I had in front of me the task of performing the entire logic, circuit, and layout design of the four chips, characterizing and transferring them to production, in six months. That’s the schedule Intel had agreed with Busicom six months earlier, but no work had been done since then! I also ended up designing and building the characterization and the wafer sorting testers as well, while the final-test tester was being purchased.”

No wonder Shima was upset.

During this April, 1970 visit to Intel, Shima had planned to check the 4004 CPU’s logic design and to see what progress had been made on the design of the other MCS-4 chips. Intel had made no progress. As a result, Shima extended his stay at Intel through October, to help Faggin complete the project.

Shima assisted Faggin with all the development phases of the project. He learned how to design integrated circuits using the methodologies that Faggin developed for Intel. He assisted with checking the logic design, the chip layout, and the Rubylith artwork for the MCS-4 chips. He also developed most of the logic design of the 4004 CPU, under Faggin’s supervision.

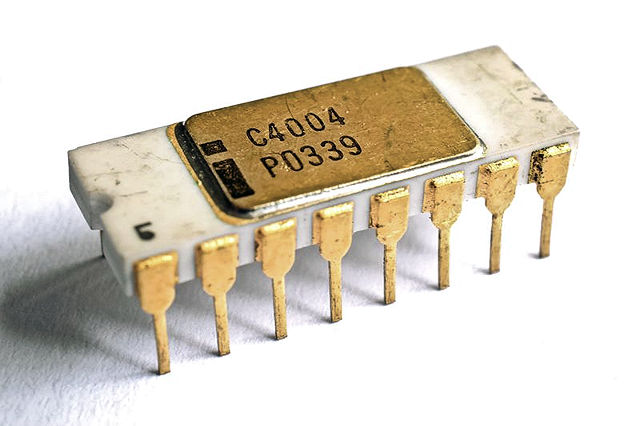

Intel crammed the 4004 microprocessor into a 16-pin DIP, because that’s the package that the company had on hand. Image Credit: Thomas Nguyen, CC BY-SA 4.0, via Wikimedia Commons

Faggin and Shima worked at a furious pace and produced working samples of the MCS-4 chipset in only nine months. Faggin brought the first 4004 microprocessor to life on a tester in January, 1971. At that point, Busicom was the only customer for the MCS-4 chipset because it had paid for the development of the four ICs. The MCS-4 chips were therefore proprietary, and the world was nearly deprived of the world’s first commercial microprocessor. Then, something happened.

It almost didn’t happen, Round 3

Here’s how Robert Noyce explained it in his 1981 article titled “A History of Microprocessor Development at Intel”:

“When completed, the new chip set could be sold only to Busicom due to contractual restrictions. But by the summer of 1971, the calculator business had become more competitive, and Busicom asked Intel to reduce prices for the calculator components. Through negotiation, Intel gained the right to sell the chip set to other customers for non-calculator applications.”

Ted Hoff and Federico Faggin both asked Noyce to cut this deal with Busicom because they both believed the microprocessor had a bright future. However, Noyce was already inclined to want this deal. According to Noyce’s biographer, Dr. Leslie Berlin, Noyce had already launched his own research project into the viability of the microprocessor as a commercial product. Here’s how Berlin describes the situation in her Noyce biography, The Man Behind the Microchip: Robert Noyce and the Invention of Silicon Valley:

“Shortly after Busicom chose Hoff’s architecture for their calculator, Noyce had quietly begun his own private version of market research on ‘a general purpose way of programming logic.’ (The term microprocessor had not yet come into use.) When he visited customers who were requesting custom circuits for certain simple logic functions, Noyce made sure at some point to ask, in an offhand way, why the customer did not just buy a computer and program it to do the task. The answer was always the same: I could do that, but it’s too expensive. The research further reinforced Noyce’s hunch that the microprocessor could be used in dozens of potential applications—not only in computers, but also in areas largely untouched by microelectronics, such as cars and home appliances—if the price was right.”

There were opposing opinions within Intel, however, according to Berlin’s biography of Noyce:

“[Director of Engineering] Andy Grove wanted the microprocessor to go away. [Marketing Manager] Bob Graham thought the company already had enough to do selling memory chips.”

Noyce had made the new agreement with Busicom by late September, 1971. Busicom got the price concessions it wanted on the MCS-4 chipset in exchange for granting Intel the right to market the world’s first commercial microprocessor. (Busicom went bankrupt in 1974.)

However, Intel did not start marketing the MCS-4 chipset to other prospective customers immediately, probably because Intel went public in October, 1971. The company was also developing the 8-bit Intel 8008 microprocessor, which it would introduce in April, 1972, and it was riding the growing tsunami of success in selling its groundbreaking 1103 DRAM, which the company had announced in October, 1970. It was a busy time for Intel. There were many other things to do.

Intel finally announced the 4004 4-bit CPU and its three support chips in an ad that ran in Electronic News on November 15, 1971. That’s the official birthday for the world’s first commercial microprocessor.

In honor of its 50th birthday, I’ll give the last word on the 4004 microprocessor’s impact to Masatoshi Shima. In an oral history, Shima said that he believed the microprocessor’s biggest innovation was to replace hardwired logic with software. Nobody knew how to do that before Intel announced the 4004 microprocessor. After the 4004 was announced, it became easy.

References:

Note: Because the Intel 4004 plays such a huge role in semiconductor history, its origins have been the subject of many, many articles over the past 50 years. Some of the information in these articles is accurate. Some appears to be less than accurate. This article is based on primary references written by the principals involved in the project and on oral histories as told by the principals. It’s also based on the Robert Noyce biography written by noted Silicon Valley historian, author, and Project Historian for the Silicon Valley Archives at Stanford University, Dr. Leslie Berlin. In my opinion, that’s the most accurate way to tell this story.

- N. Noyce and M. E. Hoff, “A History of Microprocessor Development at Intel,” in IEEE Micro, vol. 1, no. 1, pp. 8-21, Feb. 1981, doi: 10.1109/MM.1981.290812.

Masatoshi Shima, an oral history conducted in 1994 by William Aspray, IEEE History Center, Piscataway, NJ, USA. https://ethw.org/Oral-History:Masatoshi_Shima#Tedd_Hoff.27s_Initial_LSI_Design

Intel 4004 microprocessor oral history panel, Computer History Museum, April 25, 2007. https://www.computerhistory.org/collections/catalog/102658187

Berlin, Leslie. The Man Behind the Microchip: Robert Noyce and the Invention of Silicon Valley. Oxford: Oxford University Press, 2005.

I was sitting around for several years waiting for “a computer on a chip”. I’d had encounters with the PDP8 and Nova minicomputers, and fully grocked the potential of such devices.

When the 4004 came out I took one look and said “Nah! I want one chip, not 3”.

Similar for the 8008.

Then the F8. Two chips, with the program counter in both. What could possibly go wrong? (Maybe ironically, many year slater I did a mask programmed 3870 (single chip F8) design.)

By ~1974-75 I had a major project that could only be done with a microprocessor (or mini), an industrial instrument that required a shed load of floating point calculations. But by then National had their PACE, a 16 bit PMOS processor inspired by the Nova architecture, which I was familiar with. I had to write my own FP math routines.

Looking back, I am amazed at the speed of development. From the 4004 in 1971 to a pretty capable 16 bit processor in 1974. Those were heady days!

Happy to meet another Mostek 3870 user, DavidSG. We’re rare as hen’s teeth although Wikipedia claims that the F8/3870 architecture was once very popular. Nothing like the 8051 or the prolific PIC series, though.