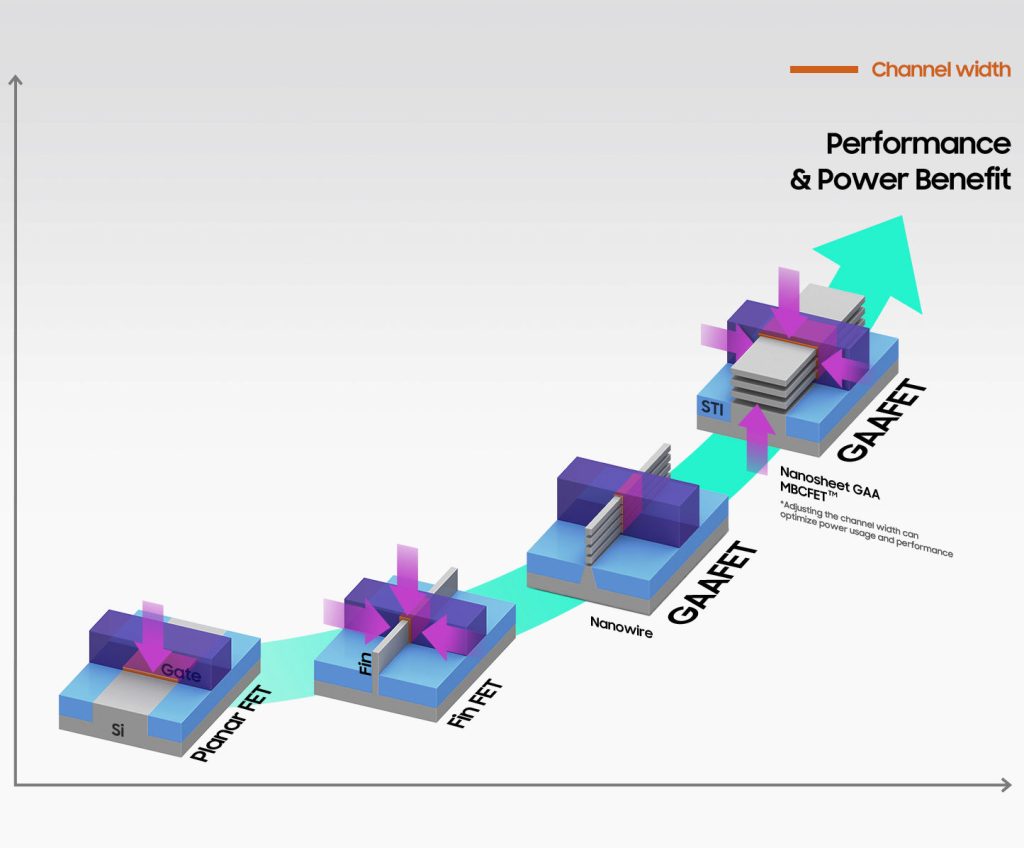

It appears that Samsung is the – ahem – first out of the gate with a gate-all-around (GAA) FET IC process technology. The company recently announced initial semiconductor production with its 3nm process node. Samsung’s trademarked name for its version of a GAAFET is “MBCFET,” which stands for “Multi-Bridge-Channel FET.” Since a picture is often worth 1000 words, and this is supposed to be a 1000-word article, here’s a picture showing the evolution of FET architecture that presently culminates in GAAFETs.

The first structure on the left is the good old planar FET, which has served the industry for 60 years. We’re still building plenty of planar FETs down to about the 28nm process node, which coincidentally is currently the most cost-effective process node, as measured by cost per transistor. But planar FETs have refused to scale much past 28nm, and so we got FinFETs, developed by Dr. Chenming Hu and his team at the University of California, Berkeley in 1999 under a DARPA contract. The advantage that FinFETs have over planar FETs is that FinFET architecture constructs a gate around three of the FET channel’s four sides. This arrangement allows the electric field from the gate to penetrate deeper into the FET’s channel, allowing better control over the current through the channel and reducing short-channel leakage.

Hu explained the reasons for the transition from planar FETs to FinFETs at a talk he presented back in 2011, in an auditorium at Cadence Design Systems. It wasn’t that we couldn’t scale planar FETs down to smaller process nodes. We certainly could draw the features needed to make these devices. But there were too many parametric compromises. First, Ioff (the FET’s off current) for planar FETs was becoming too large, which makes it very difficult to turn the FET completely off. Second, the FET’s threshold voltage, Vt, varied too much over the millions of transistors on the chip due to small variations in gate length (Lg) caused by dopant level differences across the chip, from one transistor to the next. At such small geometries, there were just a few dopant atoms per transistor, so a missing or extra dopant atom here or there makes a discernible difference. The variable Vt across the chips forced design teams to raise supply voltages for additional operating margin to compensate. In turn, the added supply-voltage margin increased power consumption for planar FET designs.

By early 2011, the FinFET’s time had arrived. That year, Intel announced the world’s first commercial FinFET node, at 22nm. Intel had a special name for FinFETs, calling them “Tri-Gate” transistors, and they used the Tri-Gate process technology to make Ivy Bridge, its 22nm version of the Sandy Bridge x86 CPU. Achronix and Altera then made waves in the FPGA industry segment a year later when they both announced that their next-generation FPGAs would use Intel’s 22nm Tri-Gate process technology to make their next-generation FPGAs. (Note: Tabula beat both Achronix and Altera to the starting line by a few months when it announced that it would use Intel’s 22nm Tri-Gate process to make its SpaceTime 3D FPGA, and EEJournal covered Tabula’s adventures in several articles, but the company closed its doors in 2015 and never became a force in the FPGA arena. Tabula’s SpaceTime 3D FPGA is another story, for another time, perhaps.)

When Altera’s FinFET-based Stratix 10 FPGAs finally appeared, they were made with a newer, 14nm Tri-Gate process at Intel. Perhaps even more important, Intel had announced its purchase of Altera by the time Stratix 10 FPGAs shipped. The long gestation of the Intel Stratix 10 FPGA is merely a lesson. It’s often not easy to migrate to a new transistor architecture. The EDA tools need to be ready to design the chips, and design engineers must learn to wield these tools to get working chips in production quantities with good yields. It all takes time and effort.

Back then, Intel hailed FinFETs as the most radical shift in semiconductor technology in over 50 years, and FinFETs served the industry well for nearly a dozen years. Now they’re running out of gas, just as planar FETs did more than a decade ago. The FinFET’s three-sided gates no longer suffice, as the transistor fins continue to get smaller and smaller.

As its name implies, the GAAFET gate structure envelops the transistor channel on all four sides, as you can see in the above image. Samsung refers to the MBCFET channel structures as “nanosheets,” which enable wider, more conductive channels than do “nanowires,” which were used by some earlier experimental GAAFET designs and appear in the figure above. Samsung can vary the nanosheet width in the GAAFETs to change the transistor’s operating characteristics as needed. The GAAFET structure permits vertical channel stacking, which has the same advantages enjoyed by multiple-fin FinFETs while consuming less real estate on the chip, because the GAAFET channels stack vertically instead of being arrayed side by side as implemented in FinFETs.

The GAAFET structure’s benefits are apparent in the announced specifications for Samsung’s 3nm process. Compared to Samsung’s 5nm process, the company’s first-generation, 3nm, MBCFET process technology can reduce power consumption by as much as 45%, improve performance by 23%, and reduce the area per transistor by 16%. A planned second-generation 3nm MBCFET process technology is expected to further reduce power consumption by as much as 50%, improve performance by 30%, and reduce area by 35% relative to the company’s 5nm process node. The improved performance and power efficiency result from the higher drive current capability and lower supply voltages made possible by the GAA transistor architecture. These are the kind of power, performance, and area (PPA) numbers that keep Moore’s Law alive. FinFET scaling alone is no longer sufficient, as was the case 12 years ago when the industry found it necessary to switch from planar FETs to FinFETs. Innovations in transistor architecture and chip packaging – including the use of chiplets – are again required to keep the Moore’s Law train on the tracks. It will always be so.

Samsung says that it will use its first-generation 3nm process technology to make chips for high performance, low-power computing applications and that the company plans to expand its use of the 3nm process to mobile processors, presumably for Samsung’s broad line of mobile phones. Although this announcement makes Samsung the first company to announce a GAAFET process node, its competitors are right there in the rear-view mirror. Intel’s first use of GAA architecture, which Intel calls “RibbonFET,” is scheduled for the company’s 20A (as in 20 angstroms) process node, and is scheduled to appear as a production process in 2024. (See “Intel Welcomes You to the Angstrom Era.”)

(Note that these Samsung and Intel node numbers, 3nm and 20A, don’t bear much resemblance to any physical reality. There are no features drawn to those specifications. Instead, these numbers refer to the gate length of a mythical planar FET, if a planar FET would work at these small geometries. They won’t.)

Intel 20A will also be the company’s first process node to move the chip’s power distribution network (PDN) from the chip’s top to the bottom, below the transistors. Intel calls this backside PDN technology “PowerVia,” and it’s a technology that should greatly reduce power-supply impedances, permitting further reduction in supply voltage and therefore power consumption. PowerVia technology will simplify signal routing on the chip’s top metal layers by removing the power-supply wiring from and making more room available for signal wires in the top metal stack. Although a process based on RibbonFETs and PowerVia is more expensive than one based on FinFETs with the usual metal stack, innovations like RibbonFETs and PowerVia are absolutely necessary for keeping Moore’s Law alive.

In June, TSMC announced that they will stay with FinFETs at 3nm and will be using GAAFETs in their N2 2nm process node, which is now scheduled for risk production in 2024, the same year that Intel plans to go into production with its 20A process technology. TSMC has also announced that it will be using backside power rails, which sounds a lot like Intel’s PowerVia technology. The company has scheduled full N2 production for 2025.

However, advanced silicon process technology delivers nothing without the right EDA tools. If the major EDA players don’t support IC design using GAAFETs, then there won’t be any tapeouts to feed the foundries. Samsung recognized this situation in its 3nm process technology announcement. The company wrote:

“Since the third quarter of 2021, Samsung Electronics has been providing proven design infrastructure through extensive preparation with Samsung Advanced Foundry Ecosystem (SAFE) partners including Ansys, Cadence, Siemens, and Synopsys, to help customers perfect their product in a reduced period of time.”

The announcement also quoted people from these EDA companies, including:

John Lee, Vice President and General Manager of the Electronics, Semiconductor & Optics Business Unit at Ansys – “Together, Ansys and Samsung continue to deliver enabling technology for the most advanced designs, now at 3nm with GAA technology. The signoff fidelity of our Ansys multiphysics simulation platform is testament to our continued partnership with Samsung Foundry at the leading edge. Ansys remains committed to delivering the best design experience for our mutual advanced customers.”

Tom Beckley, Senior Vice President and General Manager, Custom IC & PCB Group at Cadence – “Cadence worked closely with Samsung Foundry to enable customers to achieve optimal power, performance and area for this node using our digital solutions from library characterization to full digital flow implementation and signoff, all driven by our Cadence Cerebrus AI-based technology to maximize productivity.”

Joe Sawicki, Executive Vice President for the IC-EDA segment of Siemens Digital Industries Software – “Siemens EDA is pleased to have collaborated with Samsung to help ensure that our existing software platforms also work on Samsung’s new 3-nanometer process node since the initial development phase.”

Shankar Krishnamoorthy, General Manager and Corporate Staff for the Silicon Realization Group at Synopsys – “Our support for Samsung’s 3nm process with GAA architecture continues expanding, now with our Synopsys Digital Design, Analog Design and IP products, enabling customers to deliver differentiated SoCs for key high-performance computing applications.”

Although these quotes are a bit short on details, they do underscore the EDA industry’s desire to support Samsung as a semiconductor foundry. You can bet that Intel and TSMC are similarly working on golden EDA flows with these vendors for their GAAFET process nodes, because otherwise, they won’t be able to stay in the foundry game.