The walled fortress is a time honored tradition in the FPGA business. Since the beginning of FPGA time, vendors of programmable logic silicon have kept a tight grip on the tool chains that are used to program their devices. If you want to do anything with a vendor’s chips, you need the vendor’s tools and the vendor’s rules. The only exceptions have been close partnerships between FPGA companies and EDA companies to provide key bits of technology that the vendor either couldn’t or didn’t feel like developing internally.

The real reasons for this are unclear. According to the FPGA companies, it is to be sure that the bitstreams used to program their devices don’t do anything that would damage the devices or the reputation of the FPGA company. If their tools create the bitstream, they don’t end up with support nightmares trying to figure out why a customer’s chips don’t work. There are also claims that it is for security reasons. Most modern FPGAs have security logic that assures that the chip you are programming with their tools is a “real” one, and that the bitstreams used to program “real” chips are the ones intended by their customers, and not by some rogue malintent. Of course, there is a competitive angle as well. FPGA companies want their tools to help differentiate their chips, and only their chips.

The primary moat protecting this tool fortress is the venerable bitstream itself. FPGA companies keep the details of bitstreams locked down like nuclear launch codes. The vendor-provided place-and-route tools are the only things that know how to generate a bitstream that will correctly program their parts, and the only way into the chip is across that drawbridge. By controlling the entrance, the FPGA company gets control of pretty much everything that comes before – at least back to the logic netlist level.

QuickLogic has decided to end all that nonsense.

A perfectly capable open-source tool ecosystem has evolved over the past several years that includes everything one would need to develop FPGAs’ designs, program and debug processors embedded in those FPGAs, emulate SoCs, and go between popular AI development platforms and FPGA-based hardware. Key among those is SymbiFlow, an open source FPGA tool suite that is free, open source, multi-platform, and comprehensive.

Well, everything one needs – except permission. For the past several years, the open source torch mob has been bashing on the gates, reverse-engineering bitstreams and taking prisoners. Last we checked, Lattice’s iCE40 parts had been conquered (not all that impressive), as well as Lattice’s more challenging ECP5.

“Yawn. What about Xilinx?”

OK sports fans. Even the Xilinx 7-Series has been, (well, mostly) conquered. But, we aren’t here today to talk about Xilinx and whether they do or do not condone the use of obviously not-what-they-intended tools to populate their products, rather than those that their hundreds of development tool engineers have assembled over the past decades. We are here to talk about QuickLogic.

Rather than lofting flaming arrows randomly into the rebel alliance surrounding the castle, QuickLogic cleverly decided to open the gates, let them all in, and feed them dinner. Oddly, the world did not stop spinning. No technology companies were obliterated in a giant ball of fire. Most likely, nobody even got blue smoke out of their dev board. OK, that last one is a bit of a stretch.

What did happen is that designers were delighted, the open source community got a welcome boost, and QuickLogic had a shiny new development tool chain supported by a talented team they don’t have to pay. Unicorns now frolic on the lawn, and… Wait, we are getting a little carried away again.

Let’s review what QuickLogic does – namely, market ultra-low-power FPGAs and SoCs for use in high-volume, power-sensitive applications such as – just about every IoT design on the planet. And, if stand-alone chips aren’t your thing, they also break another longstanding rule by offering their technology in eFPGA form, so you can drop it right into your own chip. The QuickLogic EOS S3 MCU is an ultra low power SoC with multi-core Arm-Cortex M4, embedded FPGA fabric, and a bunch of RAM and peripherals – all bundled up in tiny packages. This device family can be customized using the aforementioned open source tool chain, and it can be prototyped using both a tiny and an unbelievably tiny development board (both of which are also open-source hardware, of course).

The “tiny” dev board is called QuickFeather, comes in an Ada-fruit “Feather” form factor, and it has all the stuff you probably need for your next edge IoT project – accelerometers, pressure sensor, and microphone, all hooked up to the EOS 3 MCU with appropriate peripherals and connectors.

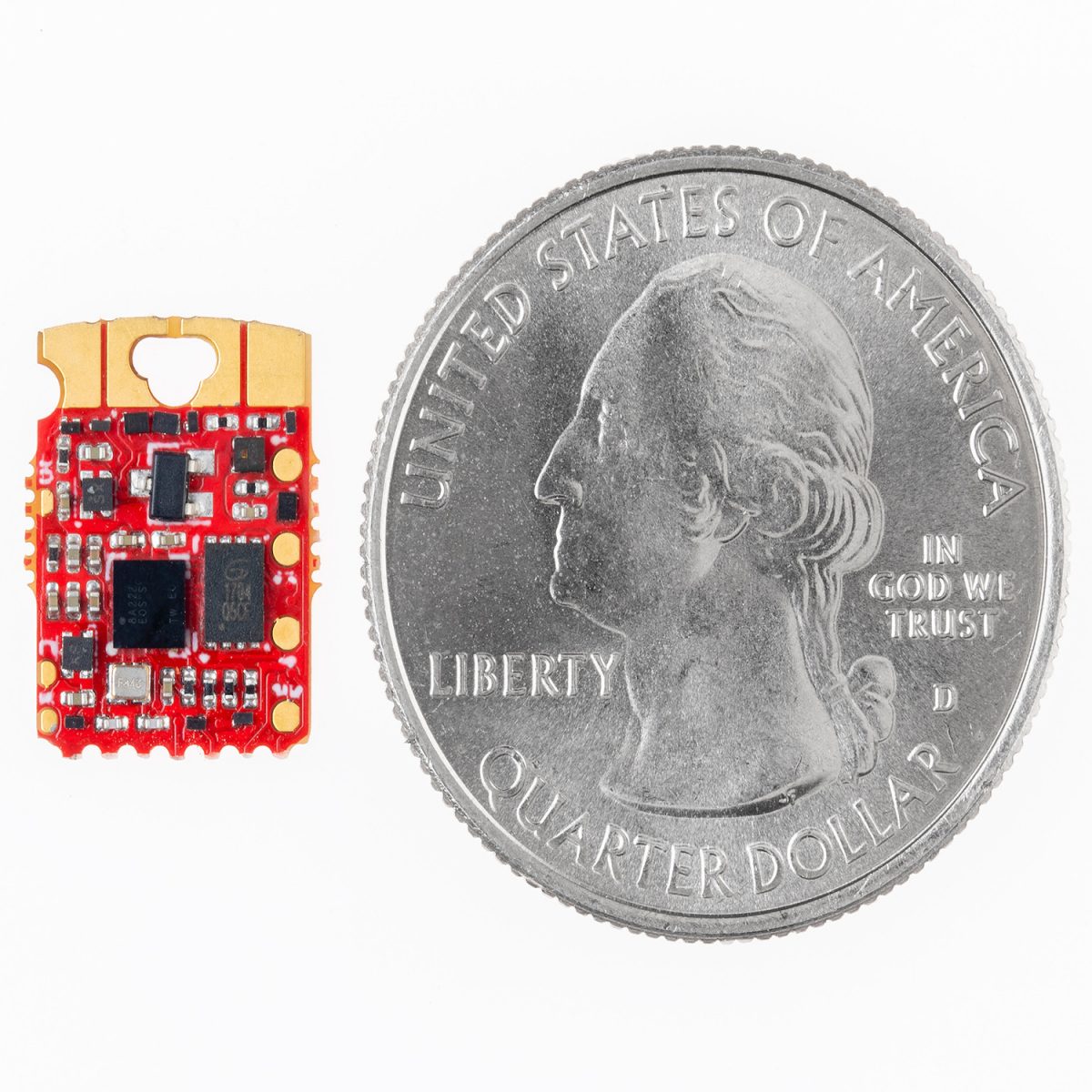

The “unbelievably tiny” dev board (we are not kidding about this part) is called Qomu. Roughly the size of your fingernail, it fits inside a USB plug and is powered by the 5V USB power. It too contains an accelerometer, capacitive touch pads, RGB LED, and of course the EOS S3 – along with 16Mbit of external flash. Also, yes–it is open source hardware.

All of this open-source-y, easy-to-design-y, disruptive stuff for creating IoT designs fits under an umbrella QuickLogic calls “QORC” for QuickLogic Open Reconfigurable Computing, developed in collaboration with Google and Antmicro. The design environment includes SymbiFlow (as discussed earlier) as well as the Zephyr RTOS, FreeRTOS, Renode development/emulation framework, nMigen Python toolbox, and MicroPython. The company also plans bridges to TensorFlow Lite and SensiML for AI development.

QuickLogic’s vision is to facilitate system partitioning in edge embedded systems, allowing compute intensive tasks such as AI inference to be offloaded/accelerated in the FPGA fabric. By embracing the open and collaborative approach, the company brings in a wealth of technology and engineering resources far larger than they could ever muster with a closed, in-house approach. The ultra-low-power, small form factor, high-volume-ready market for IoT applications including AI inference, voice recognition, video analytics and other high-value technologies is poised to grow exponentially, and QuickLogic is executing a very smart strategy to surf that wave. It will be interesting to watch.

Seems Mouser aren’t allowed to sell this product in UK?

Not the Quicklogic USB dev kit I clicked on anyway

Buxwaha Forest: Bunder Diamond Mining Issue