A futurist is a person who studies, analyzes, and makes informed predictions about the future, especially regarding trends in technology, society, business, culture, economics, or science. For example, a technology futurist bouncing around today might examine developments in artificial intelligence (AI), augmented reality (AR), robotics, silicon chip process technologies, and semiconductor packaging, and then discuss how these could reshape edge computing over the next 10 to 20 years.

Sad to relate, as much as I’d like to think of myself as a technology futurist, I fear that I fall far short of what is required. A lifetime’s experience has revealed that I shine only in predicting things after they’ve already come to pass. On the bright side, this keeps me humble (I pride myself on my humility). It also helps me appreciate the people I meet today who identified a need decades before it actually existed, spent years working on the problem, and have a solution ready to rock and roll now that the problem has finally raised its ugly head.

One such problem is powering the processors and hardware accelerators used for AI and high-performance computing (HPC) workloads in today’s data centers. I’m talking about things like CPUs, GPUs, NPUs, TPUs, and FPGAs, all of which have traditionally been powered using lateral (horizontal) power delivery. This means the processor is located in the center of the printed circuit board (PCB), surrounded by DC-DC voltage regulators and inductors that have to deliver power across the board. Meanwhile, the back of the board under the processor is jam-packed with thousands of small capacitors, desperately trying to manage high-speed voltage fluctuations caused by billions of transistors switching simultaneously.

The numbers involved are eyewatering. Assuming a 1,000W processor with a core voltage of 1V, we’re talking about 1,000A of current. And things are poised to get worse in the future, with transistor counts rising, core voltages falling, and power losses increasing.

The solution is to switch to vertical power-delivery solutions with integrated voltage regulators (IVRs) mounted under the processor, either on the backside of the board, embedded in the board, between the processor package and the board, or inside the processor package itself.

I like to think that, technology-wise, I have my ear to the ground and my finger on the pulse (I never metaphor I didn’t like), but I have to admit that I’d never even heard of IVRs and vertical power delivery until relatively recently in the scheme of things. By comparison, I was just chatting with Noah Sturcken, who is the CEO at Ferric Corporation . It seems that Noah has been working on IVRs and vertical power delivery since 2008, when he began his PhD at Columbia University.

The reason for Noah’s interest in power is that, while working on custom digital design at AMD, he realized that, despite the energy (no pun intended) he put into optimizing those designs, power integrity had a much greater impact on processor performance. It seemed to Noah that power integrity was a problem that wasn’t getting sufficient attention, especially in terms of future systems.

When Noah arrived at Columbia in 2008, his advisor was already collaborating with the Semiconductor Research Corporation (SRC) and Intel on early research into integrated voltage regulators. Intel, to its credit, had seen the writing on the wall. As supply voltages dropped below 1.0V, even 100 millivolts of noise consumed an ever-larger percentage of the total budget. Meanwhile, processor power was climbing at a super-linear rate. The arithmetic was brutal: lower voltages, higher currents, tighter margins, and mounting losses. Something fundamental would have to change.

Noah decided to make that “something” the focus of his PhD. Half of his doctoral work lived squarely in applied physics. Rather than simply using off-the-shelf magnetics, he retrofitted an ultra-high-vacuum deposition system at Columbia, complete with in-situ programmable magnetic fields. When commercial magnetic characterization equipment proved too expensive, he built his own. In short, this wasn’t a matter of tweaking spreadsheets; it was hands-on materials science.

The core problem was well known. Traditional ferrites behave nicely at high frequency because of their high resistivity and low eddy-current losses, but they can’t store much magnetic energy. Pure ferromagnetic materials like iron can store substantial energy, but their high electrical conductivity leads to unacceptable losses at the high switching frequencies required for dense integration.

The industry had long lived with this trade-off. Noah’s breakthrough was to engineer advanced ferromagnetic composite materials that deliver the best of both worlds: high magnetic energy density with low high-frequency loss. These materials enable ultra-thin inductors—on the order of a few tens of microns in total device thickness—that can switch at tens or even hundreds of megahertz without thermally or electrically degrading. That, in turn, makes true integrated voltage regulation practical at unprecedented densities.

Armed with promising lab results and industry interest (including a well-received ISSCC paper), Noah founded Ferric to commercialize the technology. The company has since grown to roughly 50 people, with strong engineering roots in both New York—where it spun out of Columbia—and Santa Clara.

Today, Ferric’s IVR chiplets integrate everything required for a complete high- performance power converter: controller, power FETs, advanced magnetic inductors, and on-chip capacitors, all in a compact tile that can be mounted on the motherboard, on the backside of the package substrate, or embedded even closer to the processor.

The devices accept a 2V intermediate rail, typically derived from the now-common 48V distribution bus used in modern data centers through a highly efficient first-stage converter. By stepping 48V down to 2V close to the processor and then using Ferric’s IVRs to generate tightly regulated sub-1V core supplies directly beneath the processor, designers dramatically reduce board-level current, I²R losses, and the thermal stress that plagues conventional lateral power delivery schemes.

Each device incorporates 16 interleaved phases operating at programmable switching frequencies in the tens of megahertz, delivering a regulation bandwidth of approximately 20MHz. That high switching frequency is not a marketing flourish—it’s what enables smaller inductors, faster transient response, and tighter voltage control. In an AI processor where billions of transistors can change state in nanoseconds, regulation bandwidth becomes as important as raw current delivery.

The numbers are striking. Ferric’s latest Fe1766 devices deliver steady-state current densities of up to 4.5A per square millimeter, with transient capability significantly higher, while maintaining conversion efficiency in the 90% range. This combination of high density and high efficiency is crucial because density alone simply shifts the bottleneck from copper loss to thermal failure. Ferric’s materials innovations enable the two to coexist.

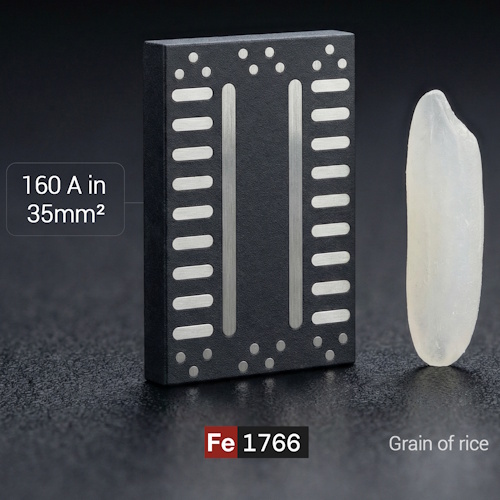

The image below shows an Fe1766 next to a grain of rice. Its 8mm x 4.4mm package, which is only a couple of hundred microns thick (about 2 to 3 human hairs), can deliver a whopping 160A sustained, and up to twice that amount for short durations.

A single Fe1766 (Source: Ferric)

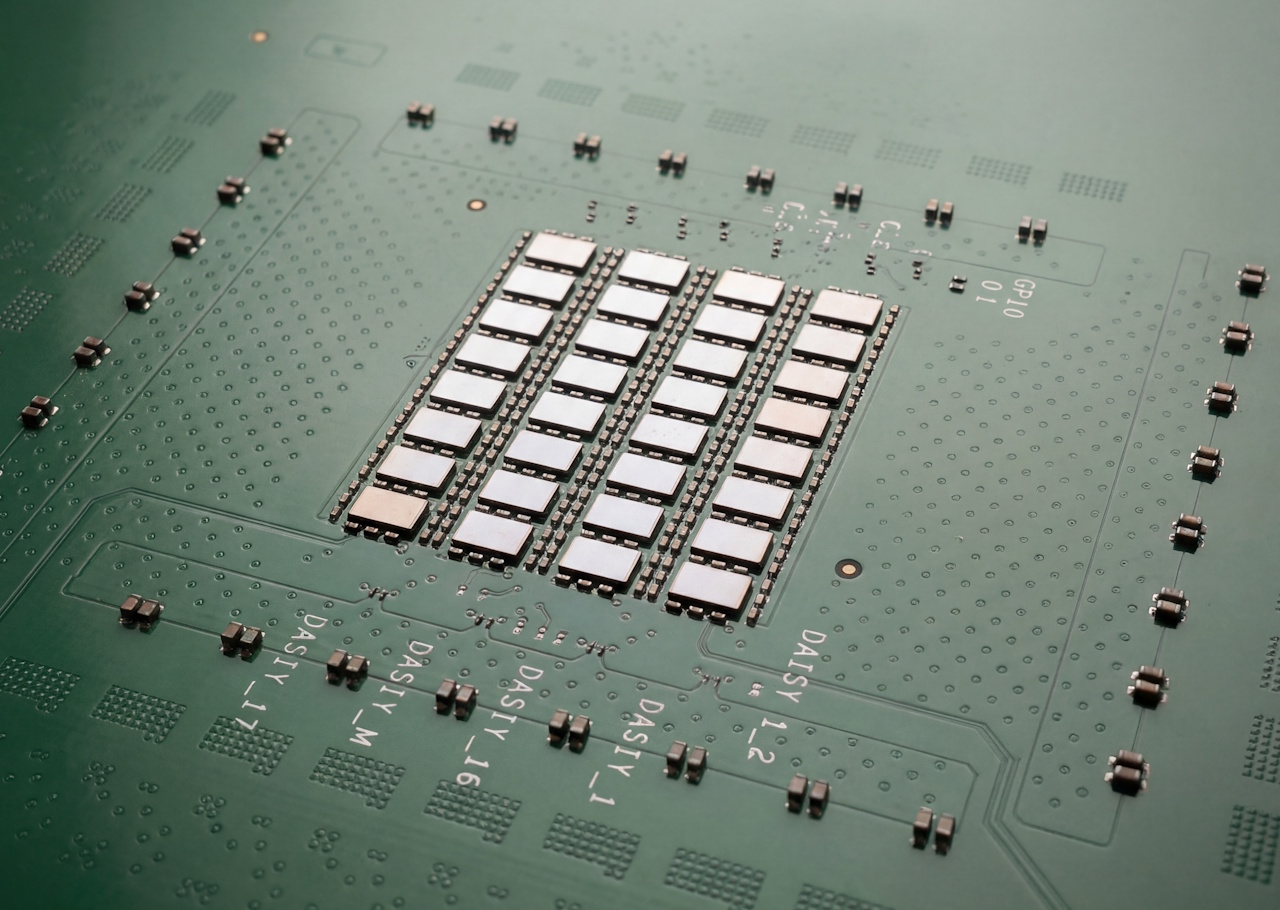

Importantly, these devices are not obliged to function in isolation. Fe1766-based solutions can scale up to >10kW by ganging up to 64 devices together. The image below shows an array of 32 IVRs mounted on the bottom of a board beneath a processor.

An array of IVRs mounted on the bottom of a board (Source: Ferric)

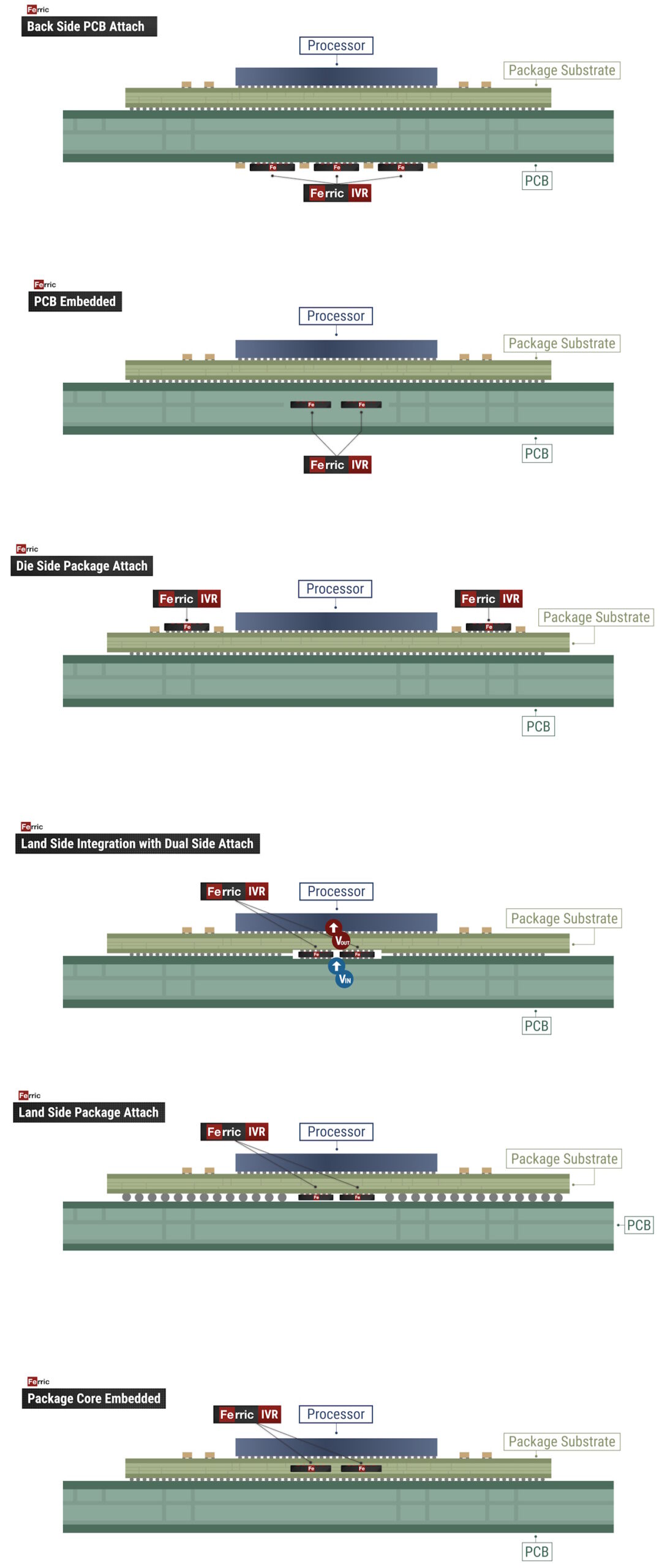

Speaking of mounting these devices, there are multiple options available to developers. The “low-hanging fruit” is to mount Ferric IVRs under the board, as shown above and illustrated at the top of the image below.

Alternative mounting strategies (Source: Ferric)

Alternative options are to embed the IVR chiplets inside the main PCB, or between the PCB and the processor’s package, or inside the processor’s package itself.

It’s important to note that Ferric’s chiplets are not science projects. Customers are actively evaluating and integrating them into CPU, GPU, TPU, and other AI accelerator packages as we speak (well, as I write and as you read, but you know what I mean).

What has changed most dramatically, however, is urgency. As recently as two years ago, IVRs were viewed by many as an interesting research direction. Today, with kilowatt-class AI processors becoming mainstream, power integrity has moved from being a secondary concern to a first-order design constraint. Engineers who once said, “We should evaluate this someday,” are now saying, “We need this designed-in today.” The threshold has been crossed.

Kilowatt-class processors are no longer theoretical. The problems Intel anticipated nearly two decades ago have fully materialized. The laws of physics have not changed, but the margins have shrunk, the currents have soared, and the tolerance for inefficiency has vanished. Vertical power delivery isn’t a curiosity anymore—it’s rapidly becoming table stakes—and the futuristic folks at Ferric have been playing this game before most of us realized there was a game to be played.