Just before Christmas, at DAC 2021, as I walked the nearly empty exhibit hall, Santa Claus leaned out of his booth and asked me if I’d like to see his thermal simulation demo. Of course, it wasn’t really Santa Claus. It was David Ratchkov, the CTO of Anemoi Software.

David Ratchkov, CTO of Anemoi Software, dressed for DAC 2021. Photo credit: Anemoi Software

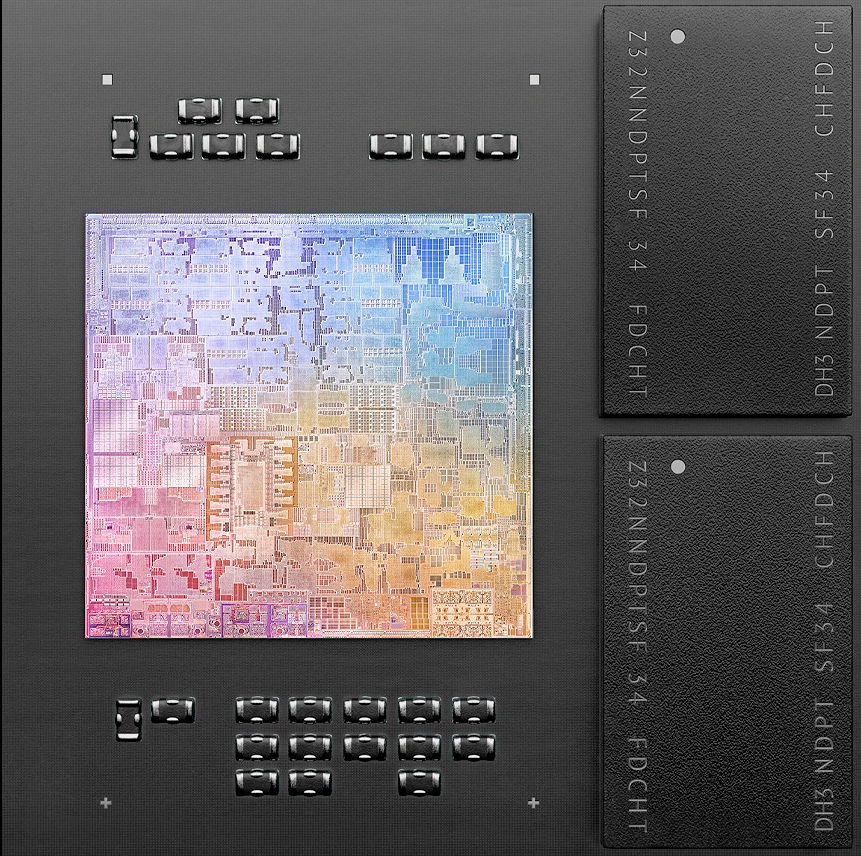

Santa’s demo involved an extremely detailed thermal simulation of an Apple M1 processor, which includes a processor die co-packaged with 16 Gbytes of LPDDR4 SDRAM on a System in Package (SiP) substrate, all sitting under a heatsink. You can see the Apple M1 processor die and SDRAM chips laid out in the image below.

The Apple M1 SiP incorporates a processor die (on the left) and two LPDDR4 SDRAMs (on the right). Image Credit: Apple

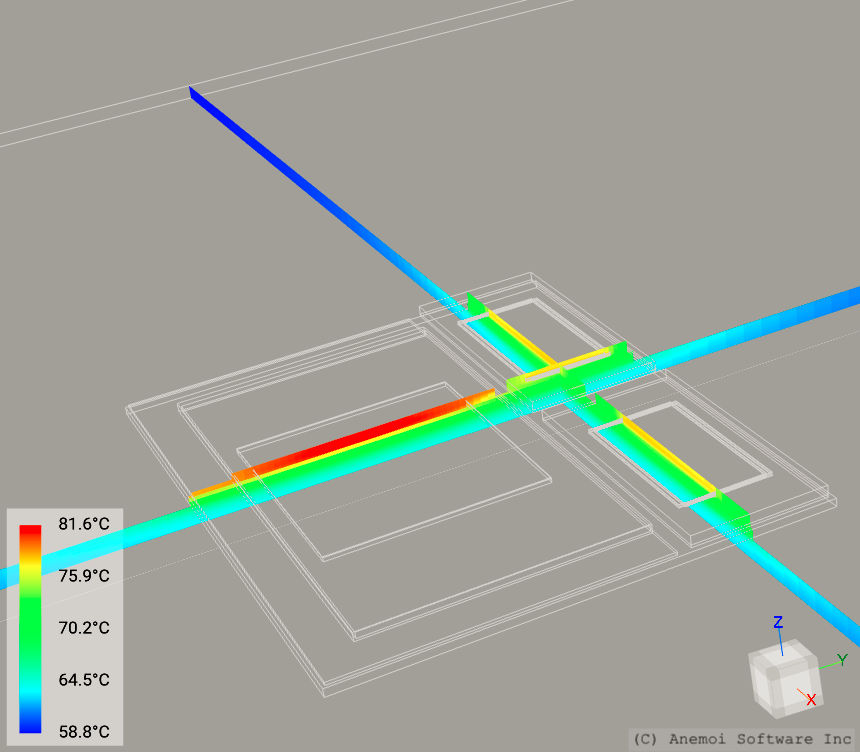

The image below shows Anemoi Software’s thermal simulation of the Apple M1 SiP. The outline of the processor die appears on the left, and the co-packaged LPDDR4 SDRAMs appear on the right.

Thermal simulation of the Apple M1 SiP. Image credit: Anemoi Software

The Apple M1 processor die is an Arm-based SoC, designed by Apple to serve as a CPU, GPU, and Neural Engine for the company’s newer Macintosh computers and iPad Pro tablets. The M1 incorporates eight Arm CPU cores. Four of these CPU cores are high-performance processors, and four are high-efficiency cores, following Arm’s big.LITTLE heterogeneous processing architectural model. The SDRAMs provide a unified memory to the CPUs, the 8-core GPU, and the Neural Engine.

Anemoi extracted the thermal and power data to build this demo from published engineering teardowns of the Apple M1. Therefore these models are somewhat less detailed than what they might be if the actual design data were available. The thermal model in Anemoi’s demo can be used for thermal simulations at the package level, but you’ll get no deeper insight about what’s happening at the block level within the chip because the Anemoi model isn’t sufficiently detailed to allow more thorough thermal simulation. However, this demo does take into account the detailed information available for the pcb design, including the board’s metal layers with their thermal conductivity, the solder balls used to attach the M1 BGA and their thermal properties, the IC package, and the bulk thermal properties of the M1 processor die.

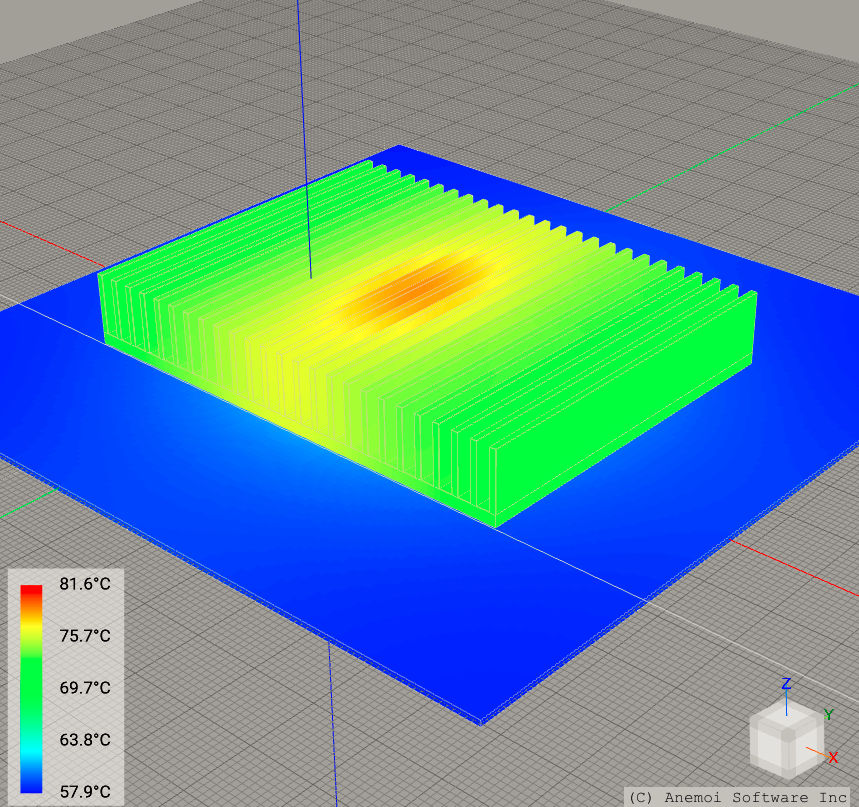

As you can see in the image below, Anemoi’s thermal simulation shows a hot spot forming within the M1 chip and within the heat sink. Ratchkov pointed out that this level of detail is useful for physical system design. For example, you can see from this simulation where you might best position a fan – at which end of the heat sink – to drive heat away from the co-located SDRAMs. DRAMs don’t like heat, so keeping them cool is an excellent idea. The Anemoi thermal simulator can take you much deeper into your design, given the right engineering data.

Heat sink thermal simulation for the Apple M1 SiP. Image credit: Anemoi Software

Santa, er Ratchkov, shared another simulation with me to demonstrate his software’s intra-chip thermal simulation capabilities. The second simulation he showed me was for a DEC Alpha processor. If you’re young enough, this processor’s name will probably mean nothing to you, and you might not even know what “DEC” means. “DEC” stands for “Digital Equipment Corporation,” which was the world’s largest and most important minicomputer vendor for about three decades. In fact, DEC literally created the minicomputer market when it introduced the first-of-its-kind, 18-bit, PDP-1 minicomputer in 1959.

Following the PDP-1’s introduction, DEC introduced many PDP minicomputer families with an assortment of data-word widths and capabilities, including the 12-bit PDP-8 families, the 16-bit PDP-11 families, and culminating in the world-dominating 32-bit VAX minicomputer product family. I learned assembly-language programming from Professor Philip Bevington on a DEC PDP-9 minicomputer. DEC made only 445 of those machines, and the PDP-9 minicomputer that I learned to program controlled a synchrotron in the basement of the physics department at Case Western Reserve University.

However, in a classic case of Clayton Christensen’s Innovator’s Dilemma, DEC was extremely late to the microprocessor party even though the company had previously disrupted the mainframe market by introducing minicomputers. You’d think that a company with that history and many, many proven, proprietary processor architectures and ISAs would dive into the microprocessor arena early and often. You’d be wrong. DEC ignored microprocessors and microcomputers for far too long – until it was much too late.

Although DEC dabbled with multi-chip and integrated implementations of its minicomputer architectures – notably the PDP-8 and PDP-11 machines – and a disastrously unsuccessful and somewhat incompatible IBM PC near-clone and VT100 terminal emulator called the DEC Rainbow 100, the company didn’t properly engage with microprocessors until 1989, nearly 20 years after the first commercial microprocessor appeared. That first machine, the short-lived DECstation 3100 workstation, was based on the 32-bit MIPS RISC architecture and could be developed only in a DEC skunkworks lab in Palo Alto, 3000 miles and an entire continent away from DEC’s mothership in Maynard, Massachusetts.

However, DEC’s real entry into microprocessors started with the DEC Alpha 21064, a 64-bit RISC processor based on a DEC-proprietary ISA and architecture. The Alpha processors were DEC’s real entry into the workstation processor wars, and the Alpha family would outperform competitive RISC microprocessors for a decade. But a high-performance processor isn’t enough. DEC continued to back the minicomputer, which turned out to be the wrong horse. The minicomputer business dried up under the onslaught of the microprocessor, and the flailing DEC was sold to Compaq Computer in 1998. All of the DEC Alpha processor IP was sold to HP in 2001, where it then vanished. DEC’s Alpha was too little, too late, despite its world-beating performance.

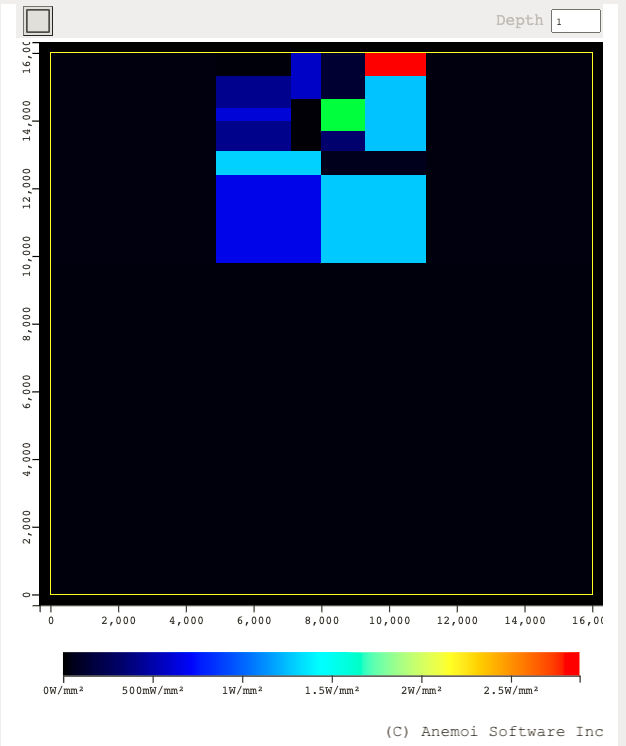

So why would Anemoi Software demo its thermal simulator on a microprocessor that disappeared 20 years ago? That’s precisely the question I posed to Ratchkov. “Because there’s plenty of detailed, public information about that design,” he replied. Makes sense, for a demo. Given the available data, Anemoi’s thermal-simulation tools provide details of on-chip heat flows, as shown in the image below:

Thermal simulation of a 64-bit DEC Alpha Microprocessor. Image credit: Anemoi Software

As you can see from the thermal plot appearing above, there’s one especially hot block on this DEC Alpha processor chip. Curiously, the hot spot is the processor’s interrupt controller, according to Ratchkov.

Because you’re reading this article on EEJournal, I’m not making much of a leap to guess that thermal simulation might not be your thing. Often, it’s mechanical or systems engineers who are tasked with thermal system design. Nevertheless, heat is an inescapable byproduct of shoving lots of electrons around at gigahertz rates. If you don’t manage that heat, then chances are you’ll get some spectacular system failures, possibly as early as seconds or minutes after flipping the system’s on-switch.

So the trick is to get to a thermal solution quickly, and that appears to be Anemoi Software’s claim to fame. The company’s Website lists four thermal case studies:

- A QSFP-DD optical module

- A GaN LED array

- A model for simulating different functional splits for chiplet partitioning

- An industrial design for an Arduino clone pcb

Build times for each of these case studies is less than 20 minutes, each, and simulation time runs from 5 to less than 20 seconds. It appears that Anemoi’s simulation tools might indeed help you find some thermal solutions quickly.

So next year at DAC, when Santa asks you if you’d like a demo, take the hint. Say yes.

In university, I didn’t do so hot in thermodynamics, so this article is welcome. BTW, some great engineering design approaches and equations for thermal management available from heat sink vendors (Wakefield, Vicor) &c.