I have a tale to tell with so many fabulous facets that I’m hard pushed to know where to start. We could come at this from so many different directions. I’ll tell you what — let’s just bite the bullet, as it were, and plunge headfirst into the fray with gusto and abandon. So, pull up your socks and hold hard onto your hat. Are you ready? Here we go…

Let’s start with Xilinx (now a part of AMD) and its family of Artix UltraScale+ FPGAs, which are based on an advanced production-proven 16 nm process and positioned as cost- and power-optimized FPGAs with best-in-class performance-per-watt. These bodacious beauties boast up to 16Gb/s transceivers for advanced and emerging protocols in networking, video, and vision (supported standards include PCIe Gen4, 10GE Vision, CoaXPress 2.1, and 12G-SDI). They also flaunt digital signal processing (DSP) slices that are optimized for both fixed- and floating-point computation, thereby supporting diverse forms of compute for image and video processing, real-time control, wireless processing, and AI inference.

As a point of interest, these are the first FPGAs I’ve seen that are available using Integrated Fan-Out (InFO) technology for small form factor packaging (9.5 x 11.5mm) that’s 70% smaller and 70% thinner than chip-scale packaging (CSP).

Now, let’s suppose you wish to evaluate one of these little rascals — where are you going to start? The best way is to use a development board that includes the FPGA itself along with a bunch of memory and a cornucopia of connectors that will allow you to connect the FPGA to your own hardware system and/or evaluate the FPGA in the context of other devices like sensors and displays.

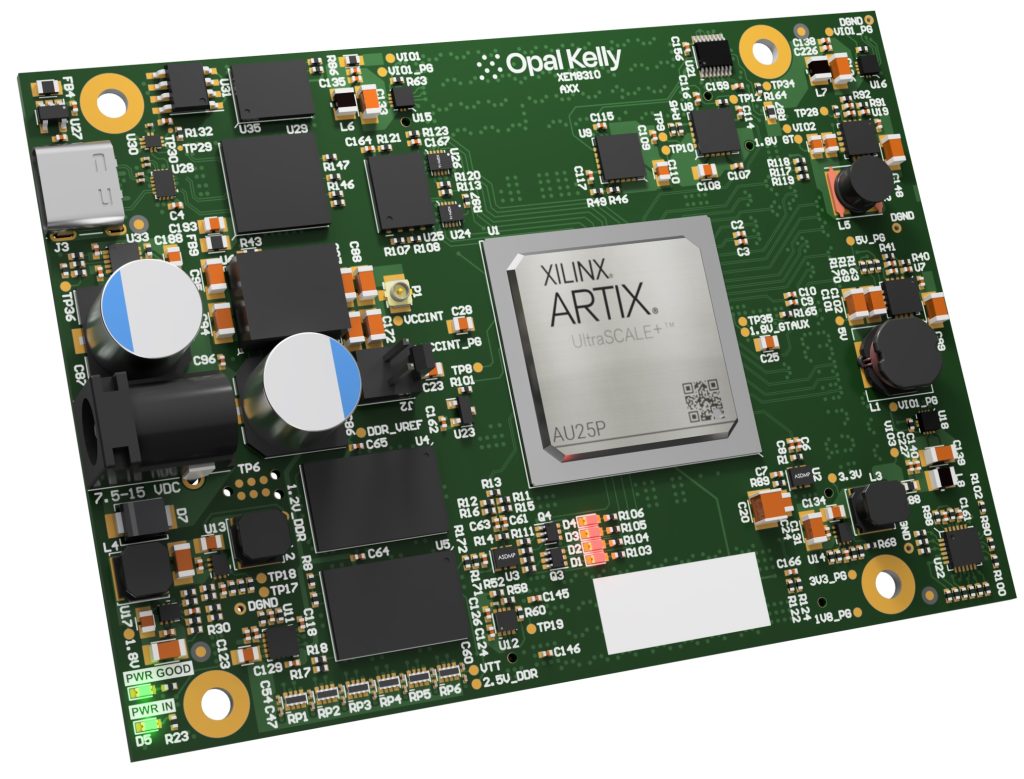

Historically, development boards for Xilinx FPGAs have been created in-house at Xilinx or in conjunction with Digilent or Avnet. This time, the guys and gals at Xilinx decided to partner with the chaps and chapesses at Opal Kelly. The result is the XEM8320, which is now the official development platform for Xilinx Artix UltraScale+ FPGAs.

The XEM8320 development platform for Xilinx Artix UltraScale+ FPGAs

(Image source: Opal Kelly)

This beast boasts an Artix UltraScale+ AU25P FPGA with 308,437 system logic cells, 4.7 Mib of distributed RAM, 10.5 Mib of Block RAM (presented in 300 blocks), 1,200 DSP slices, and 24 x 16.375 GBps transceivers.

As an aside, did you pause to wonder about the use of “Mib” in the previous paragraph, or do you already know what this means, or do you simply not care? The thing is that we have grown accustomed to using Mb (megabit) and MB (megabyte) as units of measurement for computer memory. However, this can lead to confusion because — for all other purposes — the M qualifier refers to a power of 10, so Mb and MB should really equate to 10^6 = 1,000,000 bits or bytes of memory, respectively. The problem is that most of us in the engineering world use these qualifiers to refer to quantities of memory defined as a power of 2; that is, we assume Mb and MB equate to 2^20 = 1,048,576 bits or bytes of memory, respectively.

In 1998, in order to resolve this confusion, the International Electrotechnical Commission (IEC) defined the units mebibit (a contraction of mega binary bit, symbol Mib) and mebibyte (a contraction of mega binary byte, symbol MiB) to represent 1,048,576 bits or bytes of memory, respectively. Although many engineers dislike this new nomenclature, the use of mebibit and mebibyte (and related units) is strongly endorsed by the IEEE and the CIPM and is becoming more common, but we digress…

In addition to its Artix UltraScale+ AU25P FPGA, the XEM8320 development platform also flaunts a SuperSpeed USB 3.0 Type C interface, 1 GiB DDR4-266, 16-bit wide memory, 32 MiB QSPI Flash memory (also 16 MiB of system Flash memory), 4 SYZYGY Standard Ports, and 2 SYZYGY Transceiver Ports (TXR4).

High level block diagram of the XEM8320 development platform

(Image source: Opal Kelly)

Now, before we go any further, if you don’t already know these things, this is probably a really good time to introduce Opal Kelly and SYZYGY. Also, we need to briefly familiarize ourselves with the concept of Opal Kelly’s FrontPanel software and software development kit (SDK).

Let’s start with Opal Kelly itself. These folks are famous for creating FPGA-based system-on-modules (SOMs) that are designed to provide turnkey solutions for prototypes and OEM product integration. As opposed to using these SOMs for initial development and prototyping and then redesigning everything for production, most of Opal Kelly’s customers simply integrate the SOMs into their final systems.

Of particular interest here is the XEM8310-AU25P SOM, which boasts an Artix UltraScale+ AU25P FPGA, 2 GiB DDR4, a SuperSpeed USB 3.0 Type C interface, and a single-input (8 VDC to 14 VDC) high-efficiency switching power supply.

The XEM8310-AU25P SOM (Image source: Opal Kelly)

The idea is that once you’ve completed your evaluations with the XEM8320 development platform, you can proceed to use XEM8310-AU25P SOMs for creating your prototypes and/or performing OEM product integration. Applications for this SOM include data acquisition, machine vision, edge and endpoint machine learning (ML) and artificial intelligence (AI), video and data analytics, software defined radio (SDR), digital communications and networking, cryptography, data security, and test, measurement, and instrumentation, to name but a few.

Next, let’s return to the six SYZYGY ports on the XEM8320 development platform. One of the things that makes our lives easier is the use of breakout boards (BOBs) that support components of interest like sensors, analog-to-digital converters (ADCs), digital-to-analog converters (DACs), camera modules, and so forth. These BOBs typically support a standard interface that allows them to be plugged into things like development boards, but which interface standards do they employ?

In the case of low-speed peripherals in the 1 to 50 MHz range, Digilent’s Pmod interface stands proud in the crowd. The cheap-and-cheerful 6-pin and 12-pin connectors are ideally suited to the low-cost, limited bandwidth devices presented on the BOBs. Alternatively, in the case of high-performance peripherals with eyewatering data rates, designers may opt for an ANSI/VITA FPGA Mezzanine Card (FMC) connector. These 72-pin and 200-pin FMC connectors are well-suited for use with high-performance peripheral devices that can cost hundreds or thousands of dollars.

Historically, there was no commonly accepted, widely-used interface standard in the middle of the Pmod <-> FMC extremes. In order to address this lack, several years ago at the time of this writing, Opal Kelly introduced the SYZYGY open standard for high-performance peripheral connectivity. Free to license, this standard employs low-cost, compact, high-performance connectors and low-cost cable options with pin counts that leverage available FPGA I/O. (FYI “syzygy” is an astronomical term that refers to three celestial bodies being in alignment.)

So, if you happen to have a sensor or peripheral you wish to make available to a wide audience, what do you need to do to create a SYZYGY-based BOB? Well, in addition to your own component, the simple SYZYGY connector footprint, and any discrete devices like resistors and capacitors, all you need to make your SYZYGY peripheral BOB truly SYZYGY-compliant is to add a small microcontroller (MCU) that will handle the negotiation of the voltage interface. The MCU in question is a $0.70 ATtiny from Atmel (now Microchip), and open-source software is available from the SYZYGY website.

Why do you need this MCU? Well, one of the disadvantages of Pmod is that it’s restricted to 3.3V, which was fine 10 years ago, but which doesn’t cut the mustard now. The FMC interface supports a limited form of negotiation in that the carrier can ask the peripheral what voltage it wants to use, and then the carrier provides that voltage. By comparison, when SYZYGY was conceived, its creators knew that FPGAs provide multiple banks of GPIOs, that all the GPIOs on a particular bank have to use the same voltage, that each bank may be required to be connected to multiple SYZYGY peripherals, and that these peripherals may support a variety of voltage scenarios.

In order to address this issue, SYZYGY’s creators wanted to build in more intelligence as to how voltage is negotiated between the various devices. The solution they arrived at is, using its MCU, the peripheral module can inform the carrier if it can work only at a single voltage like 1.8 or 2.5 or 3.3 but nothing in between, or if it can support a range of voltages like 1.8 to 2.5, or if it can support multiple ranges of voltages, and so on and so forth. Using the information provided by all of the SYZYGY modules on the same bank, the carrier can negotiate something that works for everybody. Pretty cool, eh?

On the bright side, some big players have already adopted SYZYGY with more coming on-board (no pun intended) as we speak. And, on the brighter side, that fact that SYZYGY is so prominently featured on the XEM8320 development platform — a platform that will probably be with us for 10 years or more — means that many more people will be exposed to the advantages SYZYGY offers. The combination of the Artix UltraScale+ FPGA from Xilinx and the XEM8320 development platform from Opal Kelly could mean that this is SYZYGY’s time to shine.

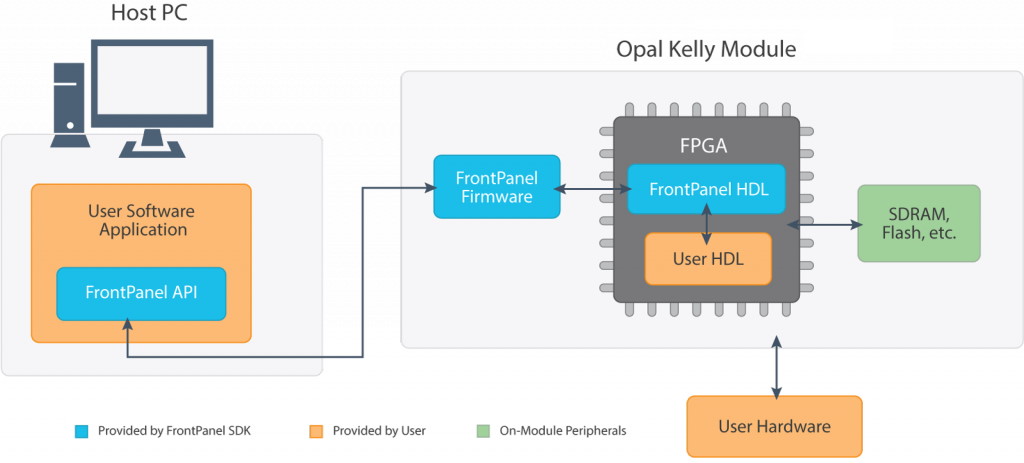

There’s one more thing we need to talk about before we continue with the XEM8320 development platform, and that’s Opal Kelly’s FrontPanel software and SDK, which dramatically accelerates the development of FPGA-based USB or PCIe devices.

High level view of FrontPanel (Image source: Opal Kelly)

FrontPanel provides an interface to your hardware that’s consistent across Windows, Linux, and Mac OS X development environments. You really have to visit the FrontPanel area on Opal Kelly’s website to peruse and ponder all the nitty gritty details. Suffice it to say that FrontPanel provides an easy way for your software application running on the host PC to communicate with the FPGA on Opal Kelly’s SOM and with your hardware on the other side of the SOM.

You can also use the standalone FrontPanel application, which lets you quickly and easily define your own graphical user interface (GUI) that communicates with your hardware. FrontPanel supports many basic UI elements including LEDs, hexadecimal displays, sliders, pushbuttons, toggle buttons, numerical entry, and checkboxes.

There’s so much more to FrontPanel than we can cover here (you may wish to take a peek at the FrontPanel Documentation). Suffice it to say that the XEM8320 is the first official Xilinx development platform to offer FrontPanel support.

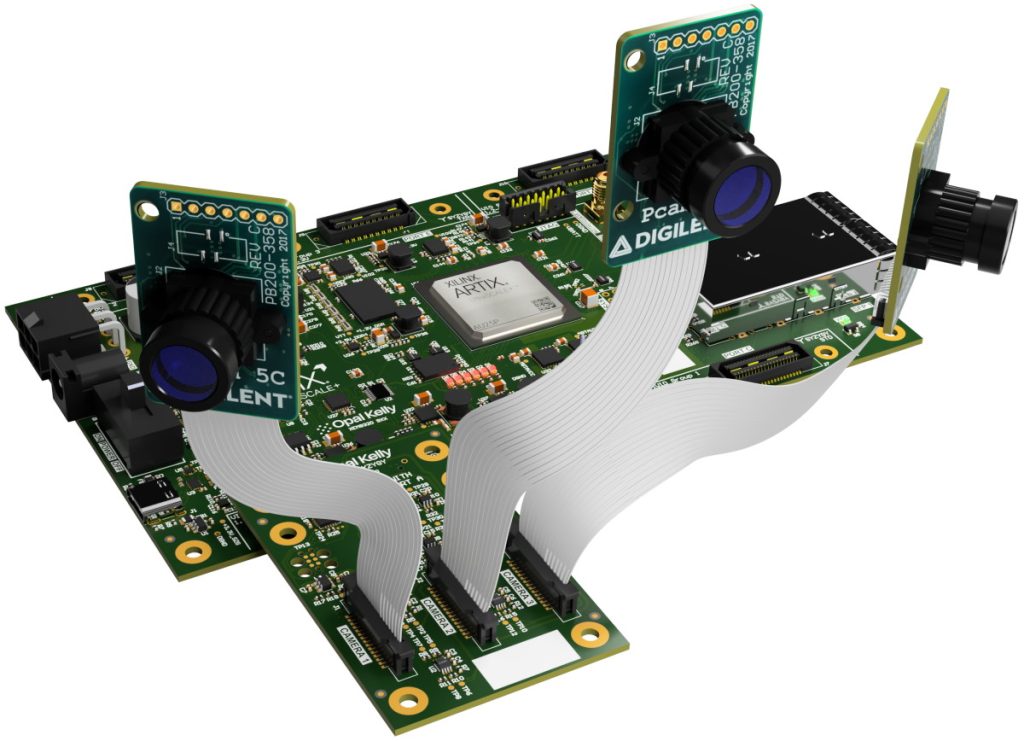

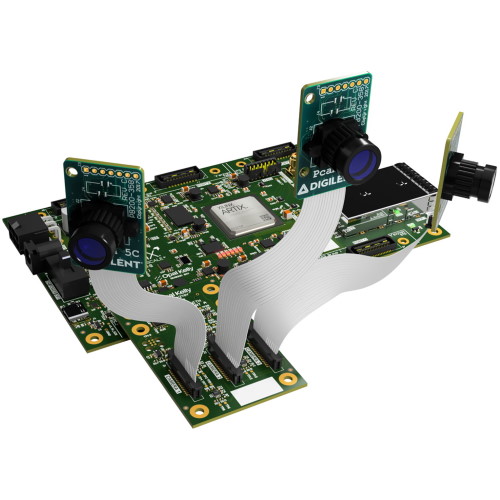

Thinking about it, this would probably be a good time to show you a couple of renderings. The first illustrates the use of a SZG-MIPI-8320 BOB sporting triple MIPI FPC connectors to connect the XEM8320 to a triad of MIPI cameras such as the Digilent PCAM. The second reflects a SZG-PCIEX4 BOB acting as a half-height PCIe (x4) host adapter card used to provide a cabled connection to one of the XEM8320’s SYZYGY transceiver (TXR4) ports.

SZG-MIPI-8320: Triple MIPI FPC connectors to connect the XEM8320 to MIPI cameras such as the Digilent PCAM (Image source; Opal Kelly)

SZG-PCIEX4: A PCI Express (x4) host adapter card to provide cabled connection to SYZYGY transceiver (TXR4) ports (Image source: Opal Kelly)

There’s so much more that I want to tell you, but I fear I’ve already waffled on too long. If you are interested in learning more, Xilinx is holding a free Jump Start Your Design with the New Artix UltraScale+ Development Platform webinar. Actually, when I say “holding,” I should say “held” because this webinar took place yesterday as I pen and post these words. But turn that frown upside down into a smile, because you can still register to watch an archived version of the webinar.

In closing, dare I ask if there are any perceptive comments or insightful questions you would care to share regarding anything you’ve read here? If you’ve actually used any of Opal Kelly’s SOMs and their FrontPanel SDK, for example, then it would be great if you could share your experiences with the rest of us.

One thought on “Artix UltraScale+ (Xilinx) + XEM8320 (Opal Kelly) = SYZYGY’s Time to Shine”