The modern world literally runs on electric motors. They’re used in every aspect of manufacturing, logistics, and transportation. Back in the earliest days of electric motors, when motors were still quite big and expensive, a motor’s mechanical output power would likely be distributed to individual workstations within a factory via a system of belts, pulleys, and drive shafts. Many late 18th and early 19th century factories already had these mechanical drive systems in place to distribute steam or water-wheel power, so it made sense to simply replace these older power sources using an electric motor to drive the existing mechanical power-distribution system directly. However, as the cost and size of electric motors decreased, it soon made more sense to build electric motors directly into the devices they powered. Electric motors quickly became ubiquitous.

Today, according to an International Energy Agency report titled Energy Efficiency 2022, “Electric motors and motor-driven systems account for around 70% of the total global electrical use of the industrial sector.” Consequently, it makes sense both economically and environmentally to drive these electric motors as efficiently as possible.

Efficient motor control has long been a target application for FPGAs because of the real-time nature of motor control and because there are many types of electric motors of varying sizes, from fractional-horsepower motors to large electric motors that drive ships and locomotives, and there are different ways of driving those motors depending on their type, size, and application. With so many varied motor-control algorithms, it’s very hard to develop a one-size-fits-all motor-control IC, which is why flexible, programmable FPGAs fit so well with this sort of control application.

AMD has now targeted motor-control applications directly with the newest member of the Kria SoM (System on Module) family. The Kria K24 SoM is based on a unique Zynq UltraScale+ MPSoC developed specifically for this motor-control SoM. Physically, the Kria K24 SoM is about half the size of a credit card, so it’s easy to design the SoM into an end product, and that’s precisely how AMD expects to see it used. Single unit pricing is $250 for a commercial-grade Kria K24 SoM and $350 for an industrial-grade Kria K24 SoM. In conjunction with the K24 SoM, AMD has also developed the $399 KD240 Drives Starter Kit, shown below in Figure 1. The company has added accelerated motor control libraries to the Vitis development environment and created development flows for motor-control applications using Python and MATLAB’s Simulink to aid in developing applications for this SoM.

Figure 1: AMD KD240 Drives Starter Kit for motor-control applications, including a Kria K24 SoM under the heat sink. Image credit: AMD

The Zynq UltraScale+ MPSoC developed specifically for the Kria K24 SoM incorporates a quad-core Arm Cortex-A53 application processor and a dual-core Arm Cortex-R5F real-time processor, 154K “system logic cells” (the method that AMD uses to measure programmable-logic capacity for UltraScale and UltraScale+ FPGA fabrics), and 132 I/O pins that can be used for connecting motors, sensors, and other subsystems. The Kria K24 SoM includes 2 Gbytes of 32-bit LPDDR4 SDRAM, and it has four USB ports and four gigabit Ethernet ports with TSN (time-sensitive networking) capabilities. TSN is used to implement real-time, deterministic Ethernet networks, which are increasingly required in industrial network environments. The TSN capabilities require using some of the MPSoC’s on-chip programmable logic to implement the required real-time hardware.

The Kria K24 SoM libraries include support for several types of motors, including induction motors, brushed and brushless permanent-magnet motors, reluctance motors, and servo motors. The library contains more than 25 accelerated and demonstration applications for the Kria K24 SoM and builds on the existing company’s existing Vitis Motor Control library. Per AMD, the following Vitis Vision Library APIs are leveraged heavily:

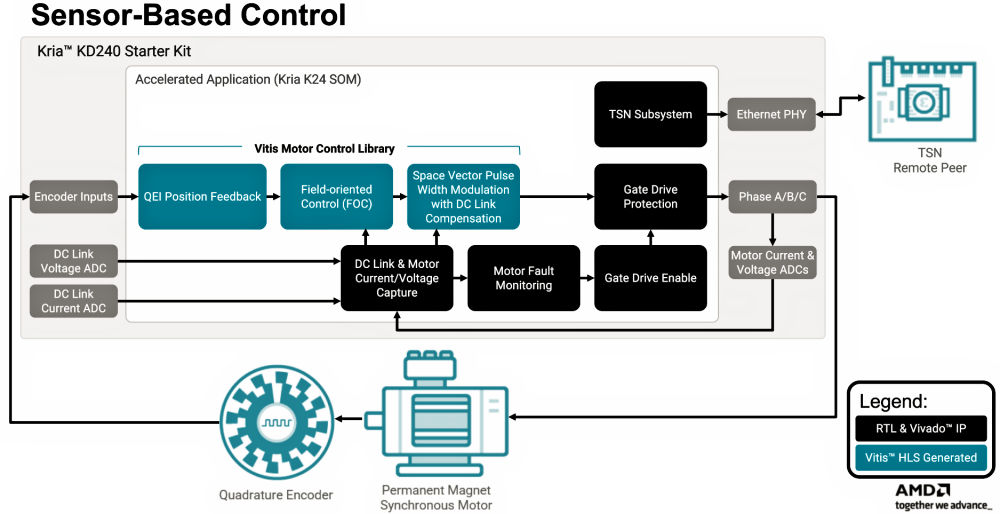

- FOC (Field-Oriented Control): Sensor-based FOC with eight control modes covering basic speed and torque control modes.

- SVPWM_DUTY: The front end for Space Vector Pulse Width Modulation (SVPWM). Used to calculate duty-cycle ratios.

- PWM_GEN: The SVPWM back end, which generates output signals based on duty-cycle ratios calculated by SVPWM_DUTY.

- QEI: Quadrature encoder interface.

AMD supplied a graphic (see Figure 2) showing how the various Kria KD240 library modules work together to create a sensor-based motor-control subsystem.

Figure 2: Block diagram of a motor-control subsystem based on the Kria KD240 Drives Starter Kit libraries. Image credit: AMD

The Kria K24 SoM also supports AMD’s Deep-learning Processor Unit (DPU), a soft-core IP block that the company developed specifically for its family of Zynq UltraScale+ MPSoCs. This DPU is a configurable computation engine optimized for convolutional neural networks. (Note: This use of the three-letter abbreviation “DPU” doesn’t correspond in any way to the predominant use of the term, which refers to a data-processing unit designed to be used in high-speed networking applications.) This AMD DPU is a microcoded compute engine built from the MPSoC’s programmable logic that supports the AI inference needs of convolutional neural networks. As such, this DPU for the MPSoC can be used to add AI inference capabilities to the motor-control algorithms implemented with the Kria K24 SoM. The library for the KR24 SoM includes a DPU-PYNQ application, which brings AMD’s PYNQ Python programming and Jupyter Notebook environments for embedded systems to the KR24 SoM.

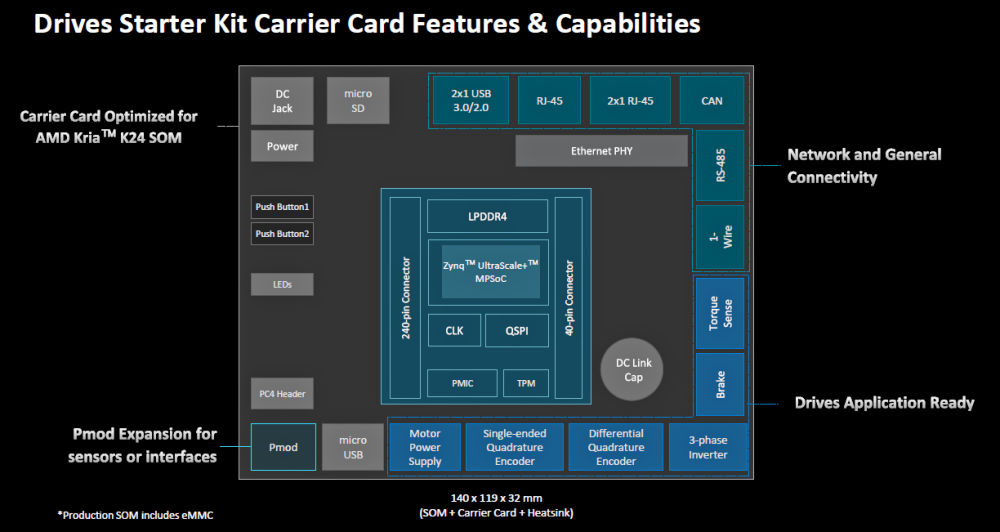

Figure 3 shows a block diagram of the KD240 Drives Starter Kit, which consists of the Kria K24 SoM and a specialized motor-control carrier card.

Figure 3: Block Diagram of the AMD KD240 Drives Starter Kit for motor-control applications, including the Kria K24 SoM, shown in the center of the board. Image credit: AMD

As Figure 3 illustrates, the KD240 Drives Starter Kit carrier card includes multiple interface ports that might be needed in a robotic or other motor-control application, including two regular USB ports and a microUSB port, three Ethernet ports, a CAN bus interface, and an RS-485 interface. Interfaces for sensors often associated with motor control include single-ended and differential quadrature encoder interfaces and a torque-sensor interface.

AMD also has plans for two motor accessory packs to augment the KD240 Drives Starter Kit. The first such pack, available now, is the AMD Kria KD240 Motor Accessory Pack, which includes a brushless DC motor assembly with a built-in quadrature encoder from Anaheim Automation and Field-Oriented Control (FOC) applications for controlling the motor. This accessory pack is designed to make it easy to develop initial motor-control applications with the KD240 Drives Starter Kit. The accessory second pack, soon to be introduced, is the REV Robotics 2-in-1 Motor Kit Accessory, which includes a REV Robotics brushless DC motor, a ball-shooter assembly (essentially a motor-controlled throwing arm), a simple robotic arm assembly, and an accelerated, sensorless FOC application for controlling the motor. This second accessory pack is clearly aimed at the various robotic competitions in which REV Robotics participates and supplies parts and knowhow.

Note: If you’d like to understand how AMD’s “system logic cells” for UltraScale and UltraScale+ FPGAs differ from plain old “logic cells,” Michael Posner wrote a nice explanation in a Synopsys blog titled “Understanding Xilinx System Logic Cells vs. Logic Cells” way back in 2015.