In many applications today, the combination of FPGA programmable logic fabric with a microcontroller is the magic sauce that brings the whole system together and makes it “smart.” The flexibility in interface, communication, and peripherals provided by the FPGA part, along with the software-programmability of a microcontroller, truly delivers on the promise of the system-on-chip “SoC” moniker for a number of smaller-scale systems.

Back when Microsemi’s FPGA group was called “Actel,” the company was among the first to offer a RISC core as IP on an FPGA. For the past decade or so, the company has offered options for licensed ARM cores in their Igloo, ProASIC, and Fusion branded families, including the soft-core ARM M0 and the faster, hardened, ARM M3. Because of the unique properties of Microsemi’s FPGAs (non-volatile, secure, and low-power), the devices have been popular in a wide range of applications that don’t require huge amounts of FPGA fabric or larger-scale embedded applications processors. If a few thousand (up to low hundreds of thousands) of LUTs and a good, solid MCU will solve your problem, Microsemi probably has a good contender for your socket.

Now, Microsemi is introducing support for the new RISC-V open processor architecture in their Igloo2, SmartFusion2, and RTG4 product lines. RISC-V brings an attractive alternative to the ARM architectures that the company has traditionally supported for a broad class of applications – particularly those where low power and security are key concerns.

What is RISC-V?

It’s important to understand that RISC-V is not a processor, or even a processor architecture (unlike ARM’s offerings, for example). RISC-V is an open instruction set architecture (ISA) defined by the RISC-V foundation (of which Microsemi is a founding member). The ISA was officially frozen “forever” in 2014, so if you write software for RISC-V today, it should run on RISC-V for eternity without the risk of requiring a port to a newer version of the architecture.

Software written for RISC-V will run on any processor that implements RISC-V, making investment in RISC-V software development nicely portable. There are four base integer ISAs: RV32C, RV32I, RV64I, and RV128I. As you might guess from the names, these represent 32-, 64-, and 128-bit machines. The “C” in RV32C indicates a 16-bit register subset of RV32I. There are also six standard extensions defined: M (integer multiply/divide), A (atomic memory operations), F (single-precision floating-point), D (double-precision floating point), G (IMAFD – general-purpose ISA), and Q (quad-precision floating point).

Anyone is free to create their own processor architecture around the RISC-V instruction set, which is what Microsemi has done with their recent announcement. The company has designed a soft RISC-V core that can be implemented efficiently in their various supported FPGAs. The IP core is royalty-free, making it a low cost option. Additionally, the RTL is available to be used in ASIC implementations, so if you have a prototype in FPGA that later goes to ASIC, your software will be completely portable across your silicon platforms.

RISC-V is designed to be a clean, simple, efficient, easy-to-implement instruction set. With fewer than 50 instructions, it’s a lot simpler than most commercial ISAs. It provides a secure and clear separation between “user” and “privileged” modes, and it’s modular – providing the small standard base with multiple standard extensions. It’s designed to facilitate easy specialization/extension with a large opcode space available for extensions and variable-length instruction encoding.

In addition to low cost and portability, RISC-V brings strong security. Because the RTL is open source, it is available for inspection and verification up and down the supply chain. In high-reliability and safety-critical applications, you can run multiple RISC-V cores for redundancy. You could even run multiple cores from different sources with different implementations, inoculating yourself from potential bugs in a hardware implementation of the architecture.

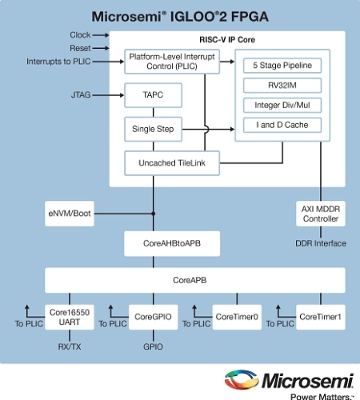

Microsemi’s initial RISC-V core is RV32IM compliant. Did you get your decoder ring calibrated above? Yep, that means it’s a 32-bit version with integer multiply/divide. For software development, it also comes with an Eclipse-based SoftConsole IDE hosted on Linux with both hardware and software debug environments, and a set of reference designs.

Microsemi’s implementation includes a 5-stage pipeline, 8K I/D cache, integer multiply and divide, 8 breakpoints, and 31 interrupts, and it performs at 1.1 DMIPS/MHz. It can boot from eNVM or SPI flash (booting from on-chip flash brings an extra level of security), and it consumes a paltry 12K logic elements of FPGA fabric and can run at 100 MHz on a SmartFusion2 (with speed grade -1). All these specs make it compare favorably with the Cortex M0 in our book, and, given the royalty-free model, it probably ends up costing less as well.

If you haven’t scoped out Microsemi’s FPGA families lately, you may be surprised at the capabilities that you can combine with the RISC-V core. SmartFusion2, for example, comes with a hardened ARM Cortex-M3 processing subsystem and has up to 150K logic elements (LUTs), 5 Mbit SRAM, and 4 Mbit eNVM. It comes with 3×36 hard 667Mbps DDR2/3 controllers, 16 5Gbps SerDes transceivers, and up to 4 PCIe endpoints. Because the devices are flash-based, they can operate as non-volatile single-chip solutions, are very low power, and have a wealth of security features. If you need a rad-tolerant chip, the company’s RTG4 FPGAs have comparable features in a radiation-tolerant version, and they can also implement the newly announced RISC-V.

Microsemi’s devices have always excelled in the high-reliability, high-security, low-power markets. Because of their unique architecture, they seldom end up competing head-to-head with conventional FPGAs from the larger suppliers. Over time, however, the company has beefed up its programmable logic and FPGA SoC offering to a point that it brings significant value to a wide range of end applications. It will be interesting to see what effect RISC-V has on expanding that space.