You know, SiTime really seems to have it in for quartz. I talked with them last month about their new Elite family, and, reviewing my notes and their presentation, it’s just slam after slam.

Not that this is inconsistent – SiTime has been working its way up the timing precision path, gradually providing MEMS alternatives to venerable quartz crystals. But, with the Elite family, they’ve entered the realm of super-precise, claiming to conquer all but the uppermost peak of clock offerings (and with an eye to taking that down as well).

It’s been a while since we talked about SiTime, back when they added temperature compensation. We subsequently covered some delicate clocking issues, mostly in the context of Sand 9, some months before their assets were bought by Analog Devices. Meanwhile, Silicon Labs has backed out of the MEMS timing arena, leaving SiTime as the overwhelmingly dominant MEMS timing player.

With each announcement, SiTime has been knocking down another precision barrier. Quartz has held on to its position for ultra-precise timing, but you’d have to expect they’re wondering when SiTime will come knocking there as well. For the present, the Elite family attacks the 0.1 ppm stability range (more on what that means in a minute).

From an application standpoint, they assign typical applications to each stability level, and the tough ones are what they refer to as NSST: networking, servers, storage, and telecom. Precise timing is particularly important in these spaces. Quartz has been able to address them, despite some less-than-ideal behaviors, while MEMS timing has historically fallen short. Getting consistent, tight timing performance from multiple dice across a wafer and across lots is not trivial. Getting them to perform unperturbed as temperature changes or in the presence of vibrations is also not trivial. These are issues that have outlasted the patience of investors in other companies. So why should SiTime be able to do any better?

They point to a fractured market where you have companies that are MEMS experts, companies that are analog circuit experts, and companies that are system timing experts. All three of these domains are critical for clocking success. SiTime claims to have all of these in-house, unlike other companies, giving them the resources to execute tight-loop convergence on increasingly challenging performance levels.

There are numerous measures that describe how precise a clock is. They boil down to these two questions: How stable is the frequency, and how stable is the phase? Getting those answers isn’t easy. (Note that these are precision questions, not accuracy questions. A clock can be super stable and precise while still being inaccurate.)

Stability means a couple of different things. The easiest one to conceive of is stability as temperature changes. This is where the compensation part comes in, of course, counteracting natural responses to temperature.

Stability over time, however, turns out to be hard to measure using classical statistics. You never converge on an average and standard deviation by adding more points in time to the data set. Each time you add a new point, the mean may simply move. So they use this thing called an Allan Deviation, and it measures stability over relatively short times to capture how squirrely a clock signal might be. You’re effectively measuring the difference between measurements at two times, and the value will change depending on how far apart those two measurements are. With a longer interval, for instance, some noise contributions will average out and become less visible.

From a practical standpoint, many systems, such as GPS, provide a timing reference. But if you lose lock temporarily, you’d like for your system to keep functioning with its internal clock until you get the reference back. So, over that short period, you want to know that the clock will remain accurate. We’re typically talking a 1- to 10-second interval here. The Allan deviation helps to quantify that short-term stability.

The whole Allan deviation thing appears to be a relatively complex topic on its own, so I’m stopping short of trying to achieve a deep dive. But it does figure into the litany of comparisons that SiTime makes between their MEMS solution and quartz.

Exactly how tight these various measure need to be depends on the application. For frequency stability over temperature, they chart requirements as:

- Industrial control – 25 ppm

- Cloud servers – 10 ppm

- Telecom exchange – 5 ppm

- Small cell base station – 0.1 ppm

For phase jitter, they list:

- Microprocessors – 175 ps

- Graphics cards – 30 ps

- Compute servers – 15 ps

- Cloud servers – 1 ps

- 100-GB Ethernet – 0.23 ps

And for Allan deviation, they show a 30,000x improvement from their first device, finally dropping below the 8×10-11 typically required for GPS. (Product Marketing Director Jeff Gao clarified that GPS customers usually specify close-in phase-noise requirements rather than Allan deviation; for simplicity, SiTime converted those into an equivalent Allan deviation number.)

In each of these examples, they say they’ve hit the most demanding point with their Elite family. The Elite brand represents a platform from which they build a number of specific “super-TCXO” and “precision super-TCXO” products. It’s a two-die solution, with the MEMS on one die and the analog on another. The MEMS die has two structures on it: the resonator and a temperature sensor used for compensation.*

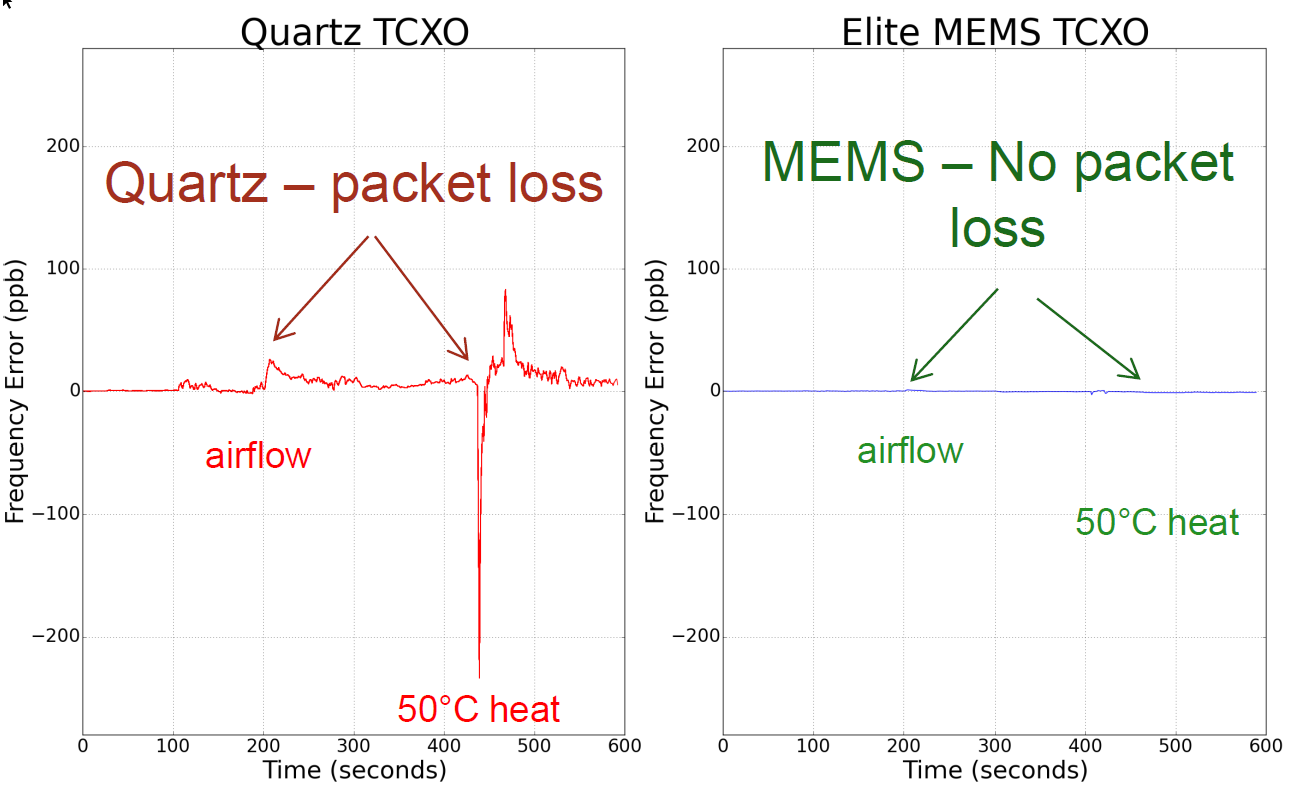

Having laid that out, they then work at smashing quartz into so much sand through a variety of application-specific performance tests. First, they show data comparing temperature response and its effect on networking traffic. The graph below suggests dropped packets with the quartz solution and no such droppage with Elite.

(Image courtesy SiTime)

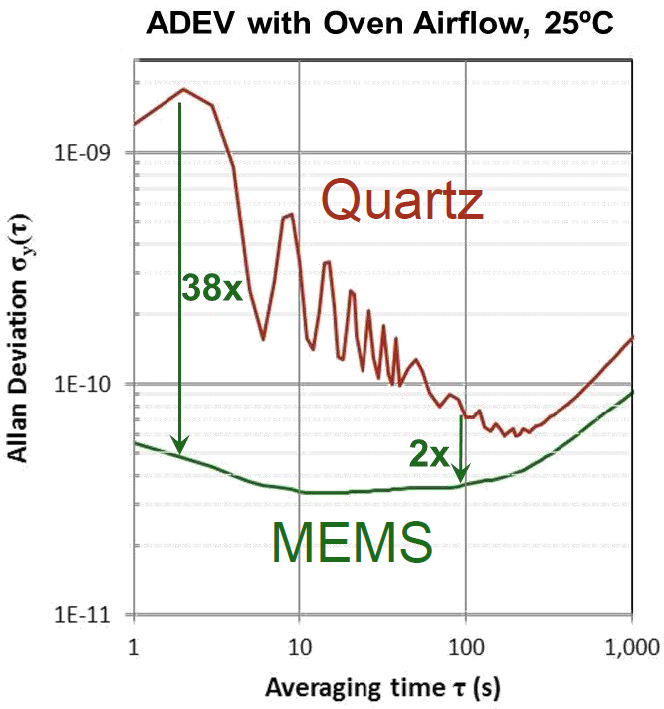

They illustrate Allan deviation under oven airflow, with a dramatically smoother and lower curve for MEMS:

(Image courtesy SiTime)

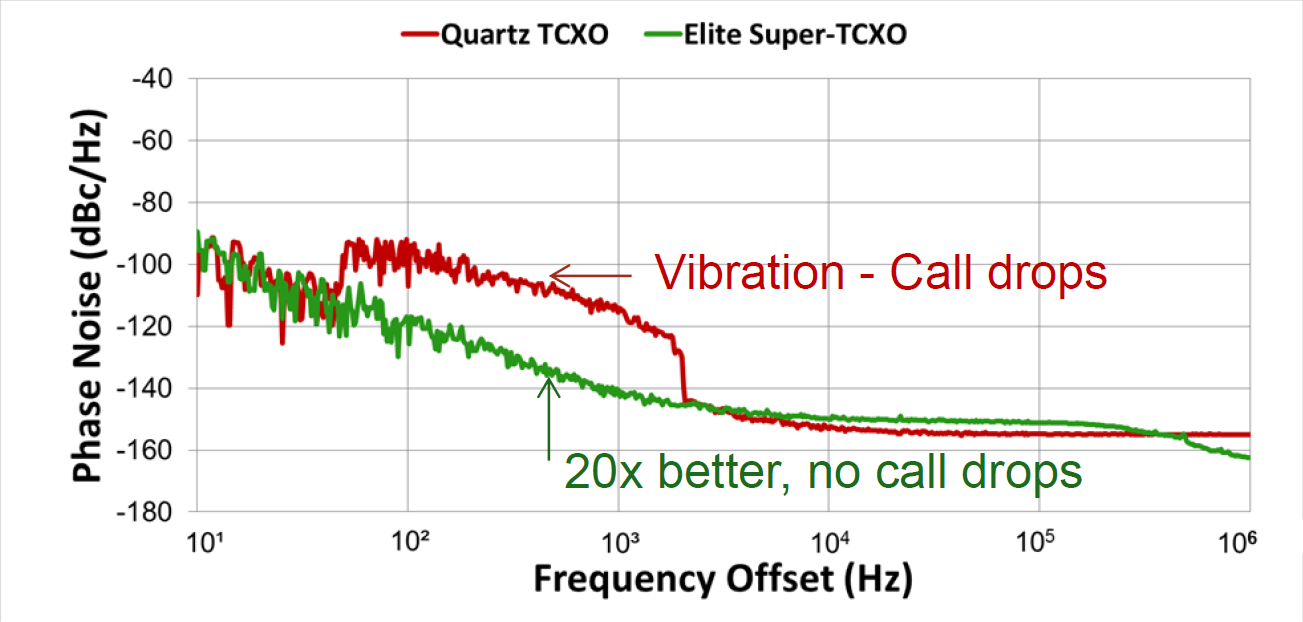

They then move to cell phones, focusing in particular on the effect that vibrations can have on the timing (due to wind against an antenna tower, for example), resulting in dropped calls.

(Image courtesy SiTime)

They also attack quartz quality, noting that Tier 1 suppliers run at a 50 dppm (defective parts per million) level, with Tier 2 suppliers cutting corners and costs with a resulting 150 dppm level. They say they’ve never had a field failure of the MEMS resonator – ever; their overall quality rate is 1.5 dppm.

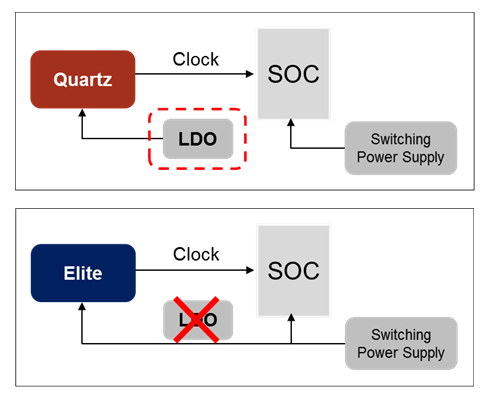

Because they say quartz is sensitive to power supply noise, a separate LDO is required – not so for MEMS.

(Image courtesy SiTime)

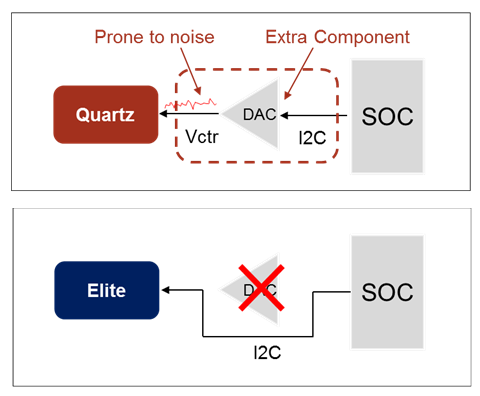

And they say that, because digital signals from the SoC, delivered via I2C, must be un-digitized** using a separate, off-chip digital-to-analog converter (DAC), the analog control output feeding back to the quartz is subject to noise as it traverses the circuit board trace from the DAC to the crystal. The MEMS version takes I2C directly into its internal DAC, reducing that source of noise.

(Image courtesy SiTime)

So, you might wonder, is quartz done? No, there’s still one more level where they retain their grip: OCXOs – oven-controlled crystals. Believe it or not, they build a small oven around the crystal and control the temperature, decoupling the crystal from the external environment. Yes, more expensive.

That said, this is on SiTime’s roadmap, so they’re taking aim. In poking around the internet in an effort to get more background, I found that there are also other technologies – like rubidium – that are available for those with a big need and lots of cash. The data I saw showed them at ten times the price of the best quartz. That will be an interesting confrontation with MEMS, should we get to that point.

We’ll have to see how far SiTime can take their technology. But my suspicion is that they’ve got plenty of business to get in the spaces they occupy now before they have to worry about those niche ultra-precise applications.

* Note that they refer to their devices with “TCXO,” and “TCXO” is technically inaccurate here, since the “X” means “crystal” – and this is MEMS, making it a “TCMO.” But because they’re competing directly for TCXO sockets, they’re using that designation for their MEMS versions.

** We don’t really have a word for that, do we? Analogized?

[Editor’s note: updated due to clarification after initial publication that the quality claim of zero failures referred specifically to the MEMS resonator, not to the entire device.]

More info:

SiTime “precision super-TXCOs”

Do you think MEMS timing will replace quartz outright?