Call it a new age of exploration. You’ve got a design to do – an analog one in particular – and you’ve got to come up with circuits that perform and that yield across the range of both operating environment and process variations.

You need to figure out whose process to use, for one thing. You may have a long-term relationship going with this foundry or that, but… wouldn’t it be nice to know what you’re missing (if anything) in those other foundries?

Then, before you commit to your circuit, you might want to do some exploration – first to pick the most promising direction and then to dial your design in. And that second bit isn’t just about sizing transistors and resistors; you also have to decide how you’re going to handle various types of variation. You may be able to center the design in a way that ensures yield and performance across the range of variation for some parameters; for others, you may need to design trim circuits to compensate for process excursions.

Or, in a completely different corner of the building, perhaps you’re supporting a group of designers by acting as the interface to your foundries. Wouldn’t it be nice if you could peruse all of the models to ensure that they’re of high quality or to compare them to each other?

Exploration can be a good way to do all of these things. You may recall our coverage of exploration in the context of designing a new process using TCAD and process simulation. Today’s discussion is the next logical step – taking a finished process, or a variety of processes available to you, and exploring how best to use them.

This is yet another discussion that originated in last June’s DAC. I had a conversation with ProPlus regarding their MEPro tool, and then, at about the same time, a new company, Intento, launched their new ID-Xplore tool. While they’re both addressing the same general issue, I perceive something of a qualitative difference between the tools, so we’ll look a bit deeper into each.

Now, you might correctly point out that everything that we’re going to discuss today can already be done without these new tools. There’s nothing to stop you from acquiring a number of process design kits (PDKs) and models and circuits from various foundries and IP companies and designers and then running variations of the circuits on a variety of processes using your favorite SPICE simulator. But there are logistics with respect to getting the PDKs. And there’s the hassle of setting up all the runs, collating the results, and then sitting back for the part where you really add value: reviewing the results and making decisions.

Looking at that manual process, there appear to me to be two big issues: one is simply a productivity one – setting up simulation after simulation and then presenting the results. Or writing a fancy script to do that. The other revolves around what I might call “content”: not so much the mechanics of running simulations, but that whole PDK thing – being able to access the technology files as well as the circuit files. And this distinction plays into how I see the two tools differing.

Let’s start with the ID-Xplore tool from Intento. There’s clearly automation in the pursuit of productivity here, tied to Cadence’s Virtuoso environment. Why Cadence? Because that’s where the money analog is.

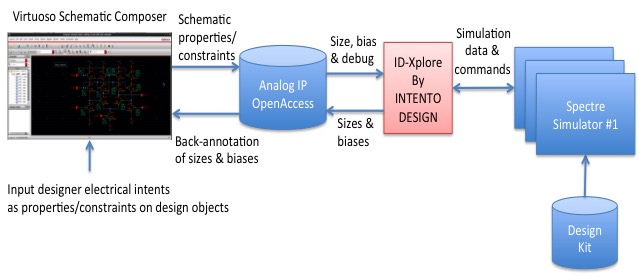

(Image courtesy Intento)

The idea is that you can place constraints or set up properties as a way of describing the intent of your exploration of your (or someone else’s) IP as stored in an OpenAccess database. ID-Xplore then handles the details of running all of the simulations. The results are then teed up for examination – in other words, you’re not telling the tool to pick the optimal solution; that’s your job. You just want to be able to see the results in an easily digestible format.

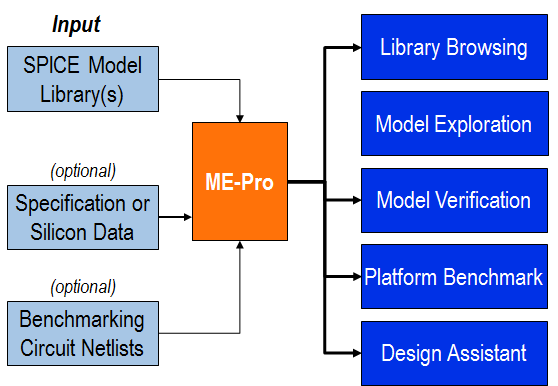

Meanwhile, ProPlus’s MEPro tool does a similar thing, but it has more of a browsy feel to it. They’ve got a database pre-populated with both foundry data and circuits. So you can rummage around through their vault, trying this circuit and that on this process and that. Many of the circuits are parameterized, so you can dial up whatever options you want before proceeding.

You’re not limited to what’s in the library; you can also use your own circuit and give it a whirl as well. Note that the tool uses its notions of layout-dependent effects to model what you put in, but it doesn’t run full DRC. Which means that you can evaluate layouts and circuits that might not be manufacturable. For what that’s worth. I guess the point is, just because you can simulate it here doesn’t mean you’re home free. The DRC police may still flag you down and cite you for various violations.

(Image courtesy ProPlus)

The pre-canned library isn’t fixed either; they’re able to keep adding to it. They’ve got a process that makes adding new circuits or models an easy thing – they can do dozens in a day.

The tool lets you explore across voltage, temperature, and process variations. And, interestingly enough, this isn’t only about finding a circuit that works – it may not even be something that your average analog designer might use. It’s just as much, if not more, about checking out the quality of the models and the PDKs – something of a quality-control mechanism. Which means it might find a home more in the offices – er – cubicles – er – seats occupied by folks acting as liaisons with foundries.

So, summarizing, you have the Intento tool, with a focus on optimizing circuits through automation, and you’ve got the ProPlus tool, with a greater focus on models and quality. The first focuses on the productivity side of things; the second on productivity and content.

You are now free to explore to your heart’s content.

More info:

What do you think of these circuit and model exploration tools?