“That’s one small step for [a] man; one giant leap for mankind.” – Neil Armstrong, Tranquility Base, July 21, 1969

So this happened. A new type of memory chip went up in the space shuttle Atlantis as part of an experiment. The astronauts opened the giant doors and exposed the cargo bay to the expanse of space. Gamma radiation, cosmic rays, extreme cold followed by intense heat as the shuttle does a “rotisserie roll,” and any number of random magnetic fields all failed to affect the little memory chip. It came back with its contents intact, because it’s a nonvolatile device. With a difference.

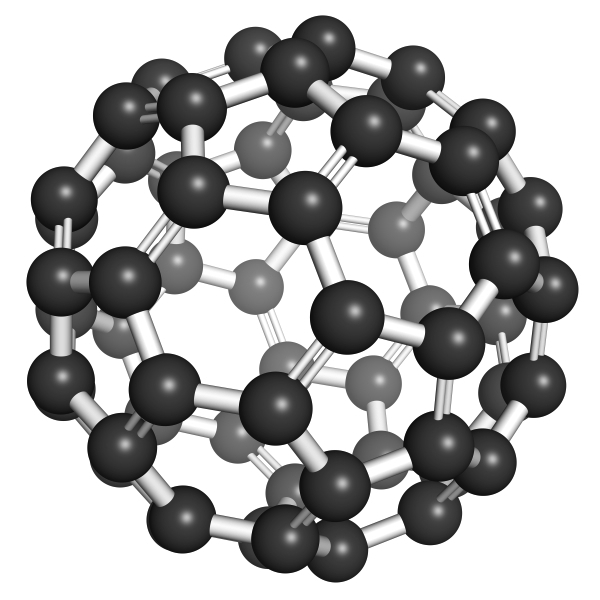

The chip in question was designed by Nantero (Woburn, Mass.) and is based on carbon nanotubes. Yup, we’re well into the 21st Century now, where we bend – literally, bend – the matter of the universe to our will. We harness the power of subatomic physics, space travel, and van der Waals’ force (whatever that is) so that we can store more selfies on our cell phones. Ain’t science grand?

So what does all this grandiosity do for you and me? Well, in a couple of years we’ll be able to buy carbon-nanotube NVRAMs and use ’em in our own designs. They’re a functional equivalent to NAND flash but promise to be faster and use far less power. They don’t promise to be cheaper, but maybe that will come later.

And how does this Space Age technology work? It’s a surprisingly comical combination of the very advanced and the ridiculously simple. Like any memory, it all starts with some sort of on/off mode flip combined with a way to electrically detect it. In DRAMs and SRAMs, we’re storing tiny electrical charges in itty-bitty capacitors. Flash memories store charges in a floating gate. MRAMs rely on magnetic materials in a north/south orientation. Hard disk drives use magnetic coatings on a platter, and so on. In each case, we’re crafting some sort of notional electronic switch.

In Nantero’s NVRAM, it really is a switch. A physical on/off switch that actually moves between the on position and the off position. None of this highfalutin nano-amp current-detection stuff. Throw the switch, Igor, it’s time to load the memory.

It’s the material that makes the switch that’s interesting. As previously mentioned, Nantero’s switches are made from carbon nanotubes – tiny cylindrical structures that measure barely 2nm in diameter. That’s about the thickness of a dozen state-of-the-art transistors. Carbon nanotubes have all sorts of interesting physical and electrical properties. For example, they’re the best electrical conductors on Earth, better even than gold or copper. They’re also the world’s best thermal conductors, so they are their own heat sinks. The material is 50 times stronger than steel, yet lighter than aluminum. And it’s made of carbon, which is fairly plentiful on this planet, as well as on most others. Not a scarce resource, then.

What Nantero does is spin-coat a sticky layer of this stuff onto a standard CMOS wafer. Just a few microns is enough. The nanotubes themselves will be orientated randomly throughout this layer. That’s okay; it doesn’t need to be pretty. It just needs to be consistently thick and evenly spread around. Then, if you put electrodes in the metal layers above and below the carbon, you can switch the nanotubes on and off simply by goosing them with a little bit of current.

In normal circumstances, carbon nanotubes are arrow-straight. They’ll be randomly scattered throughout the wafer, pointing in all directions and rarely touching one another. But pass a current through the electrodes and each nanotube will bend slightly, until it physically touches and sticks to its nearest neighbor. This is what’s known as van der Waals’ interaction. And since carbon nanotubes are extremely conductive, you’ve effectively closed a very, very small knife switch. Do this to an area filled with nanotubes, and you’ll bend enough of them to close a few hundred of these switches.

Given that nanotubes are small, you can fit a whole lot of them under each electrode. Nantero reckons that a few hundred nanotubes will fit between the electrodes, even in an aggressive 16nm process. That’s more than enough to form an effective bulk switch. It doesn’t matter if every single carbon nanotube bends and contacts its neighbors, or if only some of them do. With a few hundred potential switches in each bit cell, it’s enough if only a few dozen make contact. There’s security in numbers, in other words.

Breaking the connection relies on a different phenomenon entirely. Apply a second current to the same electrodes and you’ll induce “phonon heating,” which repels the nanotubes from one another. They essentially vibrate apart, breaking the physical and electrical connections between them, erasing the stored bit.

Both the storing/bending and the erasing/straightening processes take just a few picoseconds – so it’s fast. It also takes the same amount of time in either direction, so there’s no particular penalty for writing zeroes versus writing ones. Best of all, the energy required to tweak the nanotubes is only about 1% of that required to store a bit in NAND flash, according to Nantero. Overall, the company figures its NVRAM has the speed of DRAM or SRAM, the nonvolatility of flash, and lower energy requirements than either.

Is Nantero’s memory a MEMS? It does rely on the movement of a physical storage medium. But most MEMS require a well or cavity below the mechanism to give it room to move. That creates some manufacturing challenges and, in some cases, susceptibility to contamination and other environmental effects. Nantero’s memory is immune to magnetic fields, radiation, high or low temperatures, and vibration. It has endured more than 1012 read/write cycles in testing. Hey – if it can survive in space, it can survive almost anywhere.

The company says its patented process is compatible with everyday CMOS wafer processing and is, in fact, already working on seven commercial (through unnamed) fabs. It doesn’t even slow down the standard processing steps. All you have to do is replace your everyday jug of photoresist with a bottle of Nantero’s patented elixir. Piece of cake.

Nantero’s business model is IP licensing. The company doesn’t want to make its own chips, preferring to license the technology (and sell the goo) to existing semiconductor foundries. Soon, it will also license to fabless chip companies, so that they can include the Nantero NVRAM in their own SoC designs, then have them manufactured elsewhere, even at unlicensed foundries. The concept is pretty similar to what ARM, Imagination, Synopsys, and most other IP companies do. As usual, there are up-front licensing fees and follow-on royalties. We’re probably about two years away from seeing Nantero-enabled devices on the street. And maybe a few more years before it’s in space. Again.

Does this compare to NAND or to NOR?

NAND is not reliable. Sometimes when it is erase, it won’t erase and there are write failures.

Nor is reliable.

Or are you only comparing the density of NAND? How does it compare to new triple level NAND or Smasung’s 3D parts?