The world of system design used to be a simple place. Hardware engineers designed hardware, and software engineers wrote software. The hardware folks sat in labs, hooked things up with wires and connectors and soldering irons, and worried about current and voltage. The software engineers sat in front of computers, used editors and debuggers, and wrote, worried about, and debugged code. They played on different company softball teams, ate in different parts of the company cafeteria, and wore different styles of clothing.

Then, one day, hardware started to become a little more like software. Hardware engineers found themselves sitting in front of computers a lot of the day – writing and debugging HDL code – and then running into their labs to resume their work with scopes and soldering irons. If they were designing with FPGAs, they became even more like software engineers. It didn’t seem like a huge change, but it was the first step toward where we are today.

Today, software comprises an enormous chunk of the functionality of most system designs. On the hardware side, sophisticated SoCs do the heavy lifting, but their primary job is to execute the software quickly and efficiently – which brings us back to software engineering. Most system design teams we talk to today have a very high ratio of software to hardware engineers – often on the order of ten-to-one.

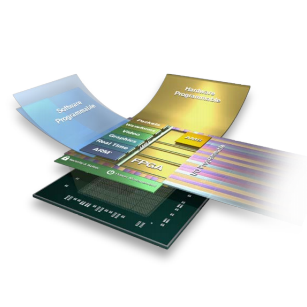

The new generation of SoCs that combine processing subsystems with FPGA fabric (we call them HIPPs or “Heterogeneous Integrated Processing Platforms”) command a whole new era of integration between software and hardware engineering. These devices (like Xilinx Zynq and Altera SoC FPGAs) blur the lines between hardware design and software design so thoroughly that a whole new approach to development tools is required. (And Blurred Lines, as we’ve just seen, can land you in litigation. But we digress.)

As we mentioned in a recent article, Xilinx has just announced the most sophisticated and complex version of these devices ever produced. The upcoming Zynq UltraScale+ family will boast quad-core 64-bit applications processors, GPUs, real-time processors, substantial memory, and all of the accoutrements of a high-end FPGA – all on one chip.

The difficult part of the hardware design – the processor architectures, interconnect busses and fabrics, memory architecture, and major peripherals – has already been done for us, courtesy of Xilinx, ARM, and other players. The part of the design that’s left for us – our special value-added part – is mostly software design. And the part that isn’t software design… is still mostly software design. That’s because one of the most important uses of the FPGA fabric (the hardware portion) is implementing accelerators for key parts of software algorithms.

For the FPGA companies designing these amazing chips, this presents a new problem. The usual hardware-centric FPGA design environment is completely inadequate for the engineering teams that will be using HIPPs. What is needed is an entirely new, software-centric design environment that encapsulates the complexities of hardware development and brings front-and-center the sophisticated software development tools required to implement applications on these unbelievably complex heterogeneous multiprocessing devices.

Xilinx has understood this problem for a while, and this week they unveiled what they call SDSoC (the latest in their SDx series of “Software-Defined-whatevers.”) The first of these was SDNet, which enabled software-defined network design by providing a high-level programming/specification environment for network design. The second was “SDAccel, which provided a programming environment that included C, C++, and OpenCL languages, combined with high-level synthesis (HLS) technology, for creating FPGA-based hardware accelerators for high-performance algorithms.

Now, SDSoC creates a programming environment like we would expect for “conventional” SoCs and ASSPs, with the additional capabilities required to take full advantage of devices like the new Zynq UltraScale+. Of course, SDSoC includes the normal things we’d expect in an embedded software development environment, such as compilers and debuggers with the special features we need to debug embedded software in a parallel heterogeneous multi-processing environment.

By the way, just that part – not your grandma’s debugger. At all.

But SDSoC is just getting started. One of the most important capabilities of an application like this on a chip is the ability to profile the application and do the software/hardware partitioning as well as the allocation of parts of the application to various types of processing elements. Profiling helps you find and identify bottlenecks or inefficiencies that lead to performance or power consumption problems and shift the offending application bits off to more appropriate resources. This performance profiling and estimation has to look at the system as a whole, not just at what’s going on with one processor at a time.

Xilinx has worked to create what they call an “ASSP-like programming experience.” Meaning, even software developers with no hardware expertise can work productively developing applications for Zynq with SDSoC. The ASSP-likeness includes Eclipse-based IDE, which is an extension to the Xilinx software development kit (SDK), a “one-click” capability to accelerate code sections into FPGA fabric, a set of optimized libraries, and support for the most popular operating systems for embedded and real-time applications such as Linux, FreeRTOS, bare-metal, and so forth.

While the profiling, debugging, and ASSP-like experience are certainly required steps for wooing design teams that might otherwise be using more conventional SoCs, Xilinx has taken SDSoC several more steps toward what we need for real productivity leaps. For certain application domains, Xilinx has pre-built optimized libraries of functions using HLS technology. These include DSP, video, fixed-point, linear algebra, BLAS, and OpenCV. With these, you can call what seem to be normal software functions and be taking advantage of optimized, power-efficient, high-performance hardware functions. Behind the scenes, your function calls are replaced with synthesizable HDL that magically (OK, it’s not really magic) compiles into the FPGA fabric of your design.

One of the more impressive (and useful) bits of functionality is an automatic system-level connectivity generator. This nifty tool analyzes the latency and throughput requirements of each of the communications interface in your design and automatically recommends (and inserts) the optimal type of interconnect for the job. Now, you don’t have to decide on your own whether simple DMA, SGDMA, or processor-direct is the best approach. The tool will make the best trade-offs for you. It automatically inserts an AXI performance monitor (APM) to provide you with detailed cache/port/memory performance information for each interface.

SDSoC is already supported with several development platforms, including Zynq development boards: ZC702, ZC706, ZedBoard, MicroZed and ZYBO. You can also build your own custom platforms using Xilinx’s Vivado along with SDSoC. The company says SDSoC is available now for early-access customers and will be rolled out soon for the rest of us mere mortals. We can hardly wait!

The most impressive feature is that you can select a function and by just a right click you can select to convert this function in HW!

I guess many VHDL/verilog designers of us, we will have to switch to C programming…