When doing a digital design, the power network is the last thing you want to worry about. It can’t be that difficult, right? You got your power and your ground and some big ‘ol FR4 acreage with nothing but copper as far as the eye can see…

Well, nothing but copper and a few vias, actually. Oh, and this part here where it gets narrow – and this part over here where there seems to be some nasty resonant frequency that drops the output… Wow, our circuit totally doesn’t work. What’s the deal?

Trying to debug power delivery network (PDN) problems without specialized tools is like cooking up a voodoo brew using only ingredients from 7-11. Fortunately, Cadence is coming out with a new set of PDN capabilities in its board design tools that will demystify the situation – a lot. The PDN Analysis tool will be part of Cadence’s Allegro board design suite, and it will offer a beginning-to-end solution to signal integrity and power analysis right where you need it – where you can do the PCB edits to correct the problems.

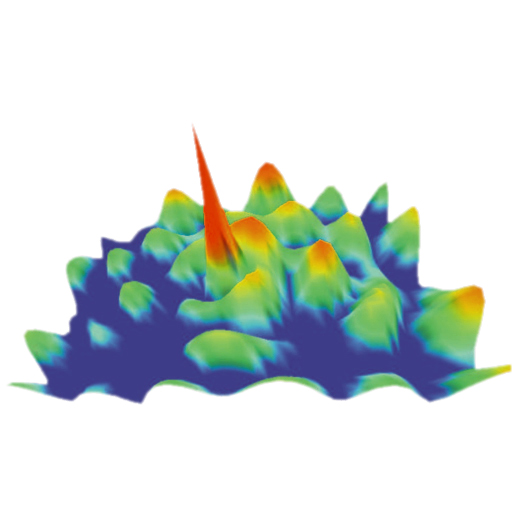

At the heart of the analysis engine is a Method of Moments (MoM) full-wave field solver that can quickly identify the eddies and whirlpools of current on your innocent-looking power plane. The Cadence solver was developed in collaboration with the University of Illinois at Urbana Champaign. The MoM solver is only a part of a broad-based set of capabilities Cadence is throwing at PDN analysis, however. The flow is designed to allow you to analyze, edit, and then re-analyze quickly – and with selectable degrees of coarseness depending on whether your goal is accuracy or speed of analysis.

Current direction with arrows. (Image courtesy of Cadence)

The idea is to locate “hot spots” of current and temperature in your layout and to guide the stackup design plane/shape split scheme. It will also help you get your decoupling capacitors “just right” so you don’t over- or under-decap your board. With this tool, you’ll be able to throw out the “needs more cowbell” method of decoupling cap design in favor of something a little more scientific.

The trickiest part, of course, is finding and fixing problems with resonant frequencies in your design. Here is where the analysis technology really shines. The tool can give both early, pre-layout feedback on resonant frequencies and detailed analysis of layouts. If you’re into fancy visualizations (they really impress the boss) the built-in graphing capabilities assure that there will be bunches of beautiful PowerPoint slides for project review meetings.

3D visualization (Image courtesy of Cadence)

For now, Cadence is just making a “technology” announcement, but we feel confident that means a “product” announcement will soon follow. Meanwhile, you’ll just have to calculate those IR drops the old-fashioned way.