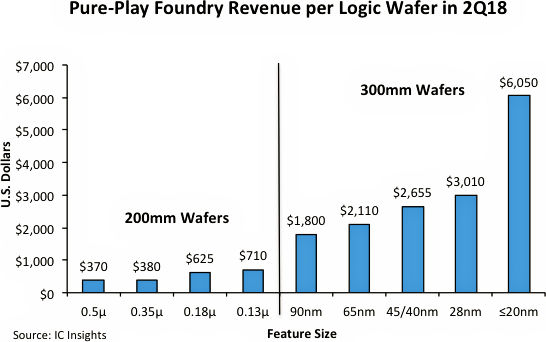

IC Insights has just published the September Update to The 2018 McClean Report, and one figure (reproduced below) puts yet another nail into the coffin for poor old Moore’s Law. Now please take care. There’s a vertical line between the 200mm wafers on the left going down to 0.13 micron lithography and 300mm wafers on the right, going down to 20nm. Per-wafer costs more than doubled going from 0.13 microns to 90nm, but the available real estate on a 300mm wafer is more than twice that on a 200mm wafer, so the cost per square nanoacre of silicon has stayed pretty constant.

(Note that the figure is labeled “revenue” but that’s from the foundry’s perspective. To the foundry customer, it’s a cost.)

But look at the jump in per-wafer costs between 28nm and 20nm (and below). There’s a sharp cost jump of slightly more than 2x, with no increase in nanoacerage. Sure, you can get more chips per wafer thanks to shrinking feature sizes, but that’s not usually what happens. The next-generation chip always has to incorporate more features. That tall bar on the far right of the graph should be drawn as a nail because it’s going into the coffin lid for Moore’s Law, which is an economic law.

As a reminder, here are the words that Moore originally used to describe the phenomenon he was seeing back in 1965:

“The complexity for minimum component costs has increased at a rate of roughly a factor of two per year.”

Moore’s Law is not just about doubling. It’s about doubling component count at a minimum cost per component.

The latest McClean Report also says, “There will probably be only three foundries able to offer high-volume leading-edge production over the next five years.” Which three? TSMC, Samsung, and Intel. The cost of joining this club is so high, it’s a safe bet that no other company is going to apply. In fact, Globalfoundries just cancelled its club membership because the dues were becoming too high. (See “Monty Python, Dead Parrots, Moore’s Law, and the ITRS.”)

For more information about The 2018 McClean Report from IC Insights, click here.

2020 is a hard year! Here is a website recommendation for a laser engraving machine, I hope there is an opportunity to cooperate. http://www.defyadequipment.com/