Seems we have so many ways of detecting the magnetic fields around us! And now we have yet another.

Some years back we covered a small company called Crocus, a maker of MRAM technology. Their MRAM cell consisted of two magnetic layers: a “pinned” reference layer and a programmable layer. The idea was that, when the layers are aligned, the tunneling resistance through the combined layers and a thin layer of dielectric between them was different from when they were anti-aligned.

So by programming the top layer to be either aligned or anti-aligned, you could store data and read it back by measuring the tunneling current through the cell (hence the resistance).

The “pinning” comes by placing the magnetic layer just over a material that, in bulk, wasn’t magnetic, but at a nano-structural level, consisted of alternating layers of atoms magnetized in opposite directions. Because they were alternating, they neutralized each other overall, but for something sitting right atop the material, it felt only the top layer, so it seemed to be magnetized. And this stabilized the magnetic layer to align and stay there.

The free layer also had a pinning material like this that stabilized it during use, but the write circuitry was able to overcome that (with the help of some heat) to allow that layer to be flipped.

So that was how it formed a memory.

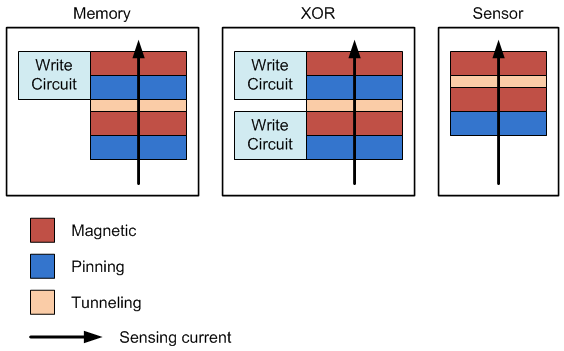

Then they figured out how to do logic with it: by making both layers programmable, they could effectively implement XOR logic. Sounded interesting, although I haven’t seen any actual product come of this idea.

Now they’ve morphed things yet one more time. In this case, they’ve removed the pinning layer from the top and they’ve taken away all the write circuitry (a huge savings). Now that top layer can simply spin away according to whichever magnetic fields it happens to be in. Its direction can still be measured by checking the tunneling current.

These three configurations are illustrated in the following conceptual, super-simplified figure.

In the memory application, the current had two values – one for 1, the other for 0. In the magnetic field detector implementation, the current can take on a continuous range of values between the 1 and 0 values.

The benefits they tout include low-power sensing, linearity good enough not to need compensation, and the ability to operate as high as 250 °C.

This actually isn’t a new thing – they’ve apparently been quietly selling this stuff for a couple years, and just completed a new round of funding. But it seemed worth talking about as an example of technology being repurposed for new markets.

You can find out more on their site…