You may recall that, about a year ago, Synopsys released a sensor subsystem. You could think of it as the IP needed to implement sensors in an SoC.

So this year they announce a “Sensor and Control IP Subsystem.” And the obvious question is, “How does this relate to last year’s announcement?”

Well, at the top level, you can think of it as an upgrade. When available in January, it will essentially replace last year’s edition.

So what’s different about it? They listed the following as some of the enhancements:

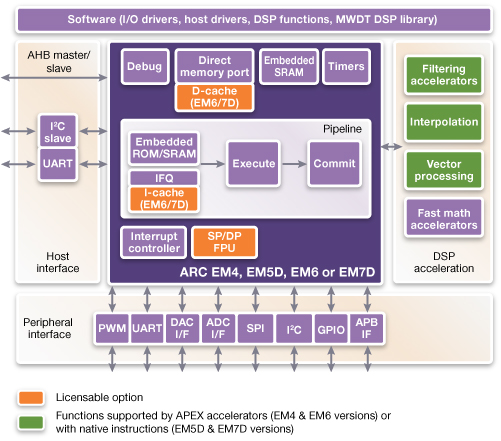

- They’ve beefed up the DSP options, including their (ARC) EM5D and EM7D cores. Last year’s subsystem could handle basic sensor processing, whereas the new one can do voice and audio and facial recognition, all of which take substantially more horsepower. They’ve also added support for the EM6 for customers that want caching for higher performance.

- They’ve added IEEE 754 floating-point math support. In case you’ve got floating point code (for instance, generated by MatLab).

- More peripherals. In addition to the I2C, SPI, and ADC interfaces that they had last year for connecting to sensors, they’ve addressed the actuator side of things by including PWM, UART, and DAC support. They also support a tightly-coupled AMBA Peripheral Bus (APB) interface.

- A big part of this whole actuator focus is motor control. So they’ve added a library of software functions for motor control. This includes “’Clarke & Park’ transforms (and inverse versions), vector modulation, PMSM decoupling and DC bus ripple elimination routines.” I honestly have no idea what those are; in this moment, I’m simply your humble (humiliated?) reporter.

Image courtesy Synopsys

You can find out more in their announcement.