ConnectOne makes WiFi modules. And they recently announced a “G2” version. Being new to the details of these modules, I got a bit confused by the number of products bearing the “G2” label as well as the modes available – were they all available in one module, or were different modules for different modes? A conversation with GM and Sales VP Erez Lev helped put things in order.

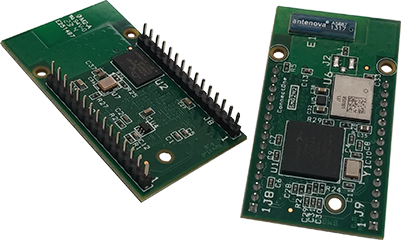

As it turns out, you might say that ConnectOne sells one WiFi module into multiple form factors. Of the different modules I saw, it was the form factor – pins vs. board-to-board vs. SMT; internal vs. external antenna – that was different, not the functionality.

There are multiple modes that these modules can take on – and these are set up using software commands that can be executed in real time. So this isn’t just a design-time configuration; it can be done after deployment in the field.

The modes available are:

– Embedded router

– Embedded access point

– LAN to WiFi bridge

– Serial to LAN/WiFi bridge

– Full internet controller

– PPP emulator

But what about this “G2” thing? Their first-generation modules were based on Marvell’s 8686 chip. And that chip has been end-of-lifed. Or, perhaps better said, it’s been 86ed. So in deciding where to go next, they settled on a Broadcom baseband chip – something they said gave Broadcom a boost in an area they’re trying to penetrate.

But the challenge was in making this change transparent to users. Existing software invokes the new chip just like it did the old one, and this took a fair bit of work. They say they were successful, however, so that upgrading from the older to the newer version takes no effort; it just plugs in.

So “G2” reflects this move to the Broadcom chip as their 2nd-generation module family. From a feature standpoint, the big thing it gets them is 802.11n support. But they also have a number of unexposed features in their controller. Next year they’ll be announcing a “G3” version, with higher performance and… well, he didn’t share all of what’s coming. But G3 will have all of the same pinouts, form factors, APIs, etc. for a seamless upgrade from G2 (or G1, for that matter).

You can get more detail in their announcement.

Image courtesy ConnectOne