IP used to refer to hardware designs that could be purchased off the shelf. Actually, at first they were designs that wouldn’t really work for any real application without a consulting contract to adapt them. But, over time, “shrink wrapped” became more viable. The idea was to save design time.

That idea still holds, but we’ve replaced one problem – design of individual blocks – with another: assembling all of the IP blocks into a complete system. And these IP blocks are more than your grampa’s simple fast Fourier transform; these are typically complete protocols that need to run a software stack.

Once assembled, the system will run the system software that’s being written for the SoC in parallel with the hardware design –software that’s separate from, and likely makes use of, the shrink-wrapped protocol libraries that may accompany the hardware IP.

So the full project development process involves hardware designers getting hardware running – first in prototypes, then in silicon. Meanwhile, software guys are coding away, using both virtual prototypes of the hardware and, eventually, the hardware prototypes that the hardware buys built.

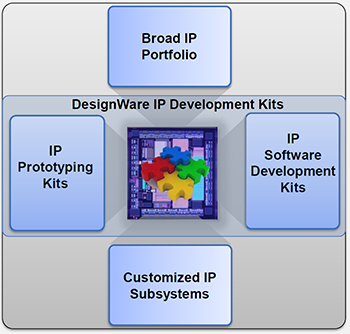

In order to accommodate this more complex flow, Synopsys has announced their IP Initiative. It involves a more holistic view of how IP is integrated into SoCs, and the idea is to make the IP and accompanying elements work out of the box so no time is wasted on things that have already been completed – all of the effort can go into integration.

The image below shows the bigger picture of what they’re trying to accomplish. It includes both existing elements (like the hardware IP) and new elements being released as of the announcement, like the prototyping kits.

The IP prototyping kits are intended for hardware engineers, and they include a working reference design out-of-the-box on a HAPS board. IP licencees will have access to the accompanying IP RTL. Meanwhile, the IP software development kits include tools and virtual platform models of the IP that, again, work out-of-the-box.

The final bit, customized IP subsystems, gets to the challenges of putting all of these pieces together and coaxing them to work. Individual IP blocks work out of the box, but assembling them into an SoC isn’t trivial. Synopsys offers services to help create subsystems out of blocks.

You can read more about their offering in their announcement.