Imagination Technologies has announced a new image signal processing architecture that they’re calling “Raptor.” The overarching concept is that the image signal processor (ISP) should no longer be a separate chip: it should be integrated into the main system SoC, along with the other related accelerators, CPU, and GPU. Raptor is IP that allows such integration. It’s targeted at next-generation image processing applications like feature identification, scalable for both low- and high-end applications.

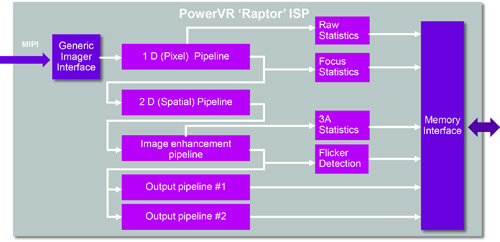

The benefits they tout come both from this integration and the fact that they provide all of the pieces required between the raw camera sensor(s) and final RGB or YUV output or an encoded image or stream. Within the ISP itself, they are able to leverage the fact that all of the technology comes from the same place – with similar compression and a unified architecture. They say that this keeps latency low and supports their “Zero-memory” approach to delivering the image to encoders and various effects accelerators.

Of course, having all of this on the SoC reduces the chip-to-chip overhead of an external ISP. The ISP also gets the process advantages of the advanced nodes typically used for an SoC.

The architecture is intended to support multiple sensors, maintaining up to four concurrent contexts. These could be front- and back-side cameras on a phone, for example, or they could be multiple cameras for multi-camera arrays, stereoscopic imaging, or “integral photography,” where multiple images are stitched together to form what can be an almost 3D image with holographic tendencies. They support up to 16-bit pixel depth, scalable to the needs of the application.

Custom processing can also be implemented by tagging the image data at various points in the pipeline and then running that data back into the pipeline. The image statistics are gathered as the image is processed; those statistics are available to the encoders, eliminating one encoding pass.

Availability is targeted for the first quarter of 2014. You can find more information in their announcement.

9 thoughts on “Next-Generation Image Signal Processor”