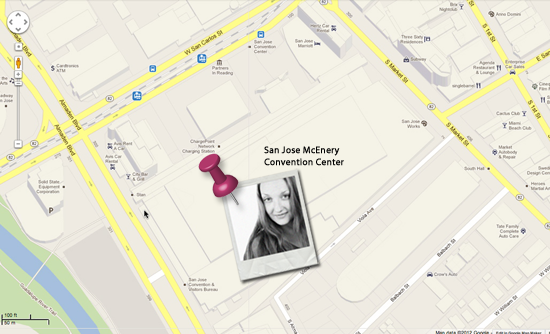

EE Journal is rolling out the most fantastic contest EVER! Yes, if I do say so myself…because this year, we are unveiling the super ultra fantastic Contest “FIND AMELIA AT ESC/DESIGN WEST 2012.” The first person who finds me and mentions a MAX V CPLD Development Kit will win a kit of their very own.

Here’s the deal: I will be trolling the expo show floor at ESC/Design West this year. The first person who finds me on the show floor will receive a MAX V CPLD Development Kit and a slew of other awesome goodies from Fish Fry’s generous sponsor Altera. In order to win, you will only need to find me and say “Hey, can I have that MAX V CPLD Development Kit?” (and not something like “Excuse me, miss, can you tell me what time it is?”) then hand me a business card and submit to an interview (mwahahaha) and the kit is yours!

Also, make sure to listen to this week’s Fish Fry (which will be live on Friday). I will be giving out some secret tips on how to find me at the show.

Click Here for more information about ESC/Design West

Click Here for ESC/Design West Expo Show Hours

And the fine print (because there’s always fine print, right?): employees of Altera (and their competitors) are not eligible. People I don’t like are not eligible.