For decades, the various companies who market printed circuit board (PCB) design software had it all wrong. The products available to us were defined not by what the customers actually needed, but by how the EDA companies could maximize revenues. The issue was this: smaller companies and individuals needed capable PCB design tools at a price they could afford. Giant corporations needed cutting-edge capabilities – at just about any price.

EDA companies responded in what seemed like a reasonable way. They began selling two levels of board design tools. “Enterprise” PCB design tools boasted every possible advanced feature. “Desktop” PCB design tools included the basic capabilities needed to design a circuit board, and not much else. The price difference between the two platforms was enormous. EDA companies could “go broad” with their low-cost desktop solutions while still milking millions from their well-heeled enterprise customers.

The flaw in this strategy, however, was their lack of understanding of the actual needs of the market. The desktop/enterprise model was based on the idea that “advanced” board design was the purview of giant companies, while smaller firms and individuals would be working on more basic designs. But, in fact, some of the most sophisticated systems are designed by small companies and small teams. Issues like signal and power integrity, small form factors, heat dissipation, dense multi-layer routing, cost, manufacturability, and so forth span designs across the gamut of team sizes. By reserving the advanced capabilities for enterprise customers, EDA companies were depriving smaller teams of the tool technology they needed.

Clearly, EDA needed to find a new way to differentiate the enterprise and desktop tool suites. The first thing that came to mind was to focus on team size – giving enterprise customers the facilities to distribute and manage complex designs across large, possibly geographically distributed teams with centralized administration and library management. Desktop customers could then be given some of the most advanced design capabilities, simply without the additional “enterprise” collaboration features.

It turned out that this model was somewhat flawed as well. Even though both small and large engineering teams were doing advanced design, they were populated by distinctly different types of engineers. Large teams had specialists – people who focused on layout, signal integrity, library management, thermal analysis, and so forth. Small teams had “tall-thin” engineers – who spent time on almost every aspect of the system design. It turns out that the tool capabilities required by a full-time specialist in layout, for example, are different than those needed by the engineer with broader responsibilities who spends only a small fraction of his time on layout. Enterprise customers needed advanced capabilities with all the options laid bare. Desktop customers needed those same advanced capabilities, but encapsulated in wizards with reasonable defaults to reduce the ramp-up time when the “tall-thin” engineers switch from one task to another.

Layered on top of this paradox of EDA packaging was the realization that teams are not just designing boards – they are designing products and systems. The days of the isolated board design environment are giving way to the higher-level system design suite, integrating a number of tools to enable a more comprehensive view of product design that goes well beyond the borders of the board. This final mandate pushed the PCB tool market toward dramatic change.

Unfortunately, most of the EDA companies had enterprise and desktop tools with entirely separate code bases that came from completely different sources. Mentor and Cadence both originally got into the desktop business by acquisition, and their enterprise and desktop offerings had little in common. This made the challenge of responding to new market demands considerably more difficult.

This week, Mentor Graphics announced the next major step in a revamp strategy that they announced over a year ago. The strategic change is substantial – a re-factoring of the enterprise and desktop offerings, a consolidation of much of the underlying code base, and a level-up from a focus on board design to a more comprehensive system/product design scope. Mentor is the largest supplier of PCB tools worldwide, and the overhaul contains similar elements to product line changes by major competitors like Cadence, Zuken, and Altium.

As announced in 2015, Mentor’s PADS “desktop” offering now comes in three flavors: Standard, Standard Plus, and Professional. “Standard” includes the basics of schematic capture and layout, and the lowest price point. “Standard Plus” throws in constraint management, additional layout capabilities, and simulation, for an additional price. “Professional” brings the most advanced capabilities, including the layout engine, from the enterprise-level Xpedition system to the desktop market.

Now, Mentor is announcing the addition of new analog/mixed-signal (AMS), power integrity, high-speed analysis, and thermal analysis products to the PADS portfolio. These new modules bring more of the so-called high-end features to the desktop domain.

The entry-level (aka “free”) AMS package is called AMS Cloud. As the name implies, it is a cloud-based exploration/simulation system, complete with user community. You just create your design and start analyzing. AMS Cloud also allows you to share your design as well as to download designs others have shared. So, you might not even have to create a new design in the first place.

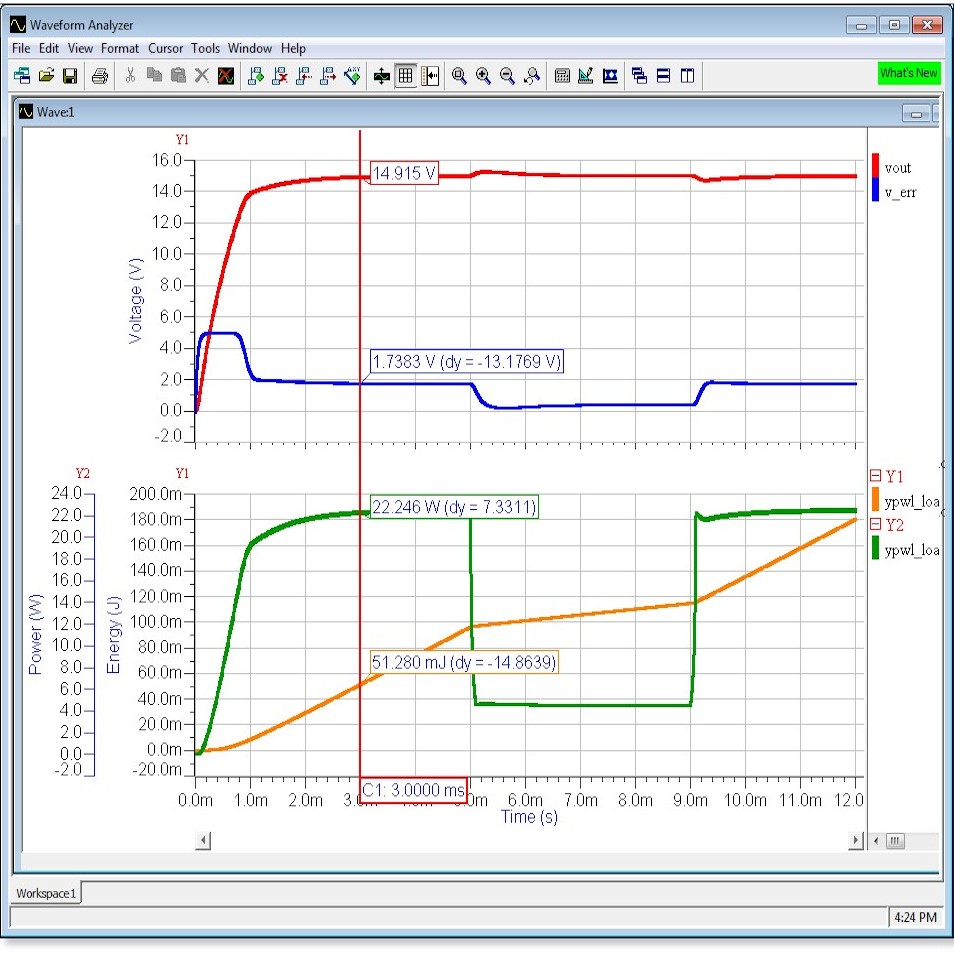

Of course, you can then download your AMS Cloud design into the full-blown (aka “not free”) PADS AMS Design Suite. AMS Design Suite is a full-fledged analog and mixed-signal design creation and analysis environment right in the PADS system. The AMS Design suite allows both analog and digital simulation of VHDL-AMS topology exploration with Mentor’s HyperLynx. The AMS simulation includes DC Bias, time-domain, and frequency-domain simulations, and a number of extended analysis capabilities such as multi-run parametric sweeps, sensitivity, Monte Carlo, and Worst Case analysis.

Power integrity (PI) analysis is accomplished by PADS HyperLynx DC Drop – an approachable PI tool that identifies problems in the power delivery network. These issues are increasingly common in today’s high-density designs where a number of factors conspire to perforate and restrict the flow of current through what used to be wide open power planes. The tool quickly provides feedback on the location of power bottlenecks, and tight integration with PADS allows problems to be easily resolved.

There are two high-speed analysis modules in the new announcement: DDR simulation, and Electrical DRC, Validation, and Sign-off. PADS HyperLynx DDRx, as you’d expect, focuses on the signal integrity and timing issues specific to DDR, which has become important in most mainstream designs today. PADS HyperLynx DRC is an electrical DRC, validation, and sign-off tool, which provides a way to catch common but hard-to-find issues such as traces crossing voids and traces changing reference planes.

Finally, there is a new thermal analysis module called PADS FloTHERM XT, which allows hardware engineers to perform thermal analysis of their designs. FloTHERM XT uses a 3D computational fluid dynamics solver to analyze both steady-state and transient thermal behavior. It allows import of mechanical objects such as heat sinks and enclosures to complete the model for thermal analysis beyond the scope of the PCB.

Together, these announcements track Mentor’s PCB strategy transition from the old, board-centric, high-end/low-end model to the new, much more inclusive, system/product-centric desktop/enterprise model. In the process, the company appears to be consolidating technology development into a more consistent code base, which should improve the overall quality and evolution of both the desktop and enterprise solutions.

And exactly the same problem occurs for FPGA synthesis, place and route software … and FPGA/EDA companies get it wrong. Including mentor.

The majority of design wins come from Tall/Thin engineers … the big companies have specialists.

Tall/Thin engineers often need access to many of the same features … just without a several million dollar EDA budget.

Hi..i am new here. First of all thanks for sharing this helpful article here. I just want to know something about this “Power integrity (PI) analysis is accomplished by PADS HyperLynx DC Drop – an approachable PI tool that identifies problems in the power delivery network. These issues are increasingly common in today’s high-density designs where a number of factors conspire to perforate and restrict the flow of current through what used to be wide open power planes” that what factors you are discussing about here?

[url=http://www.7pcb.com/PCB-Assembly-Service.php]pcb assembly[/url]