Mechanics and electronics have historically lived far apart. To do the former, you go get a mechanical engineering degree, which has very little in common with the electrical engineering degree you need for electronics. The few areas of overlap are usually ones where one side must begrudgingly learn something from the other side for the sake of appearing well rounded. I personally was never happy about going to lab at 8 AM to watch pieces of metal fail.

Of course, the two must intersect in the real world. While much of technology used to be mechanical, we’ve shifted to translating the mechanical information to electrical information as early as possible, and then we do the rest of the work in circuits. That used to mean analog circuits, since the world is analog, but this has been overtaken by the desire to get into the digital realm as soon as possible. So today’s systems deal with the world via a brief stay in the mechanical arena, followed by a brief stay in the analog domain, followed by lots of work done digitally, the result of which goes back out the same way in reverse.

The interface between the mechanical and the electrical is the realm of the transducer, which literally means something that leads (-duce) across (trans-): you’re leading information or energy from one domain into the other. It acts as a nice interface, insulating each side from the other and minimizing that area where understanding of both domains is needed.

But, as with everything technological, it’s all got to get smaller. We’re used to seeing ever-tinier circuits, but, on the mechanical side, shrinkage has also been a factor in the area of micro-electro-mechanical systems (MEMS). While a purchased MEMS unit will involve both the electro- and the mechanical elements, traditionally they’ve been made separately and have simply been attached together in a package. But interest in integrating both mechanical and electrical components on a single monolithic wafer has grown dramatically.

At ISSCC a few weeks ago, a number of transducer-oriented papers were presented, several of which involved MEMS. We’re going to feature a series of articles on each of those with the intent of exploring the different kinds of devices as well as looking at the issues addressed in the presentations. But, in advance of that, it seems fitting to establish some basic MEMS background and, in particular, to cover the combination of CMOS and MEMS.

So the intent of this article is to explore this union of two specialties. Since, for us, CMOS is more familiar than MEMS, we’ll start by briefly reviewing what the mechanical part of MEMS is all about; then we’ll throw CMOS into the mix to see how that affects things. We also need to look at how one would actually go about designing such a hybrid system. Finally, we’ll take a scan of companies operating in the CMOS MEMS space.

Fowl: MEMS 101

Let’s say you want to build a concrete-lined in-ground pool with a concrete diving platform in your backyard. Here’s a novel, if impractical, way you could do it.

First, you dig a big hole the size and shape of the pool you want. Rather than using a backhoe or shovel for any of your digging operations, you mask and blast. So first you cover the entire backyard with a sturdy protective layer of some kind, leaving an opening where the pool will go. Then you blast the entire backyard with air or water or something that will gouge out a hole in the unprotected part of the yard.

With the protective covering still in place, you then spray the entire yard with a layer of concrete. This forms the walls of the pool, but it also covers the rest of the yard. You solve that by lifting the covering and the concrete on top of it, leaving only the pool lined with concrete.

Next you fill the pool with sand. After it’s full, you build a box around the yard as high as the top of the diving platform; you fill that entire box with sand up to the level of the underside of the platform.

Now you re-cover the yard (buried in sand) except for the spot where the diving platform will mount to the pool; blast a hole in the sand for the platform support pillar. Spray a layer of concrete that fills the hole (and covers the yard), removing the excess by removing the covering. Lay a bit of plastic over the fresh remaining concrete at the top of the pillar to protect it from sand contamination.

Now, moving very quickly, before the concrete has any chance to dry, you fill the box the rest of the way with sand and, masking with a new cover layer, blast a hole the shape of the actual platform itself, one end of which will be over the support pillar you just created. Once the blasting is done, you can remove that layer of protective plastic on top of the pillar.

Now spray more concrete to form the platform, letting the new wet concrete form a strong, solid joint with the still-wet pillar concrete underneath so that the pillar and platform together become a single unit. You again remove the excess concrete with the covering and let the remaining concrete cure.

You now have a pool and diving platform formed strictly by laying sand, masking, blasting, and depositing concrete. There’s only one remaining step: take out a hose and wash away all of the remaining sand. That will empty the pool, restore the yard, and, critically, remove that last bit of support from the free end of the platform – a step known as “release.”

And with that, you’ve created a cantilever.

Change materials and replace the hoses with various etches, and you’ve got a MEMS cantilever. Of course, the details are all-important. Different materials behave differently. If your cantilever has to have certain elastic or resonant properties, you may need exotic materials.

Depending on the materials used and how they’re deposited, you may be left with residual stress that can warp or buckle some of the components. Or you might even want a certain amount of pre-stress built into the structure. So annealing steps may be required to ensure correct function, good yield, and high reliability.

Balancing all of these factors, then, you can create a unit that takes some mechanical phenomenon and derives an electrical signal from it. That electrical signal will typically be processed on some other integrated circuit, attached by good old-fashioned wire bonding.

Mating fish and fowl

Things get more complicated if you want to get the circuitry and the mechanical bits closer together, ideally, on the same wafer. At its most basic level, this means you’re going to be fabricating both diffusion layers and mechanical layers, along with their attendant wiring and support structures, in an extended series of processing steps. The details of how that happens, however, can vary widely.

First of all, why do this? In some cases, reduced interconnect can produce a higher-quality result. Other times it’s simply a size and cost equation. Rather than making two wafers and taking the space to bond them together, you can use on-die interconnect in less space and with less electrical overhead.

But this equation doesn’t always work. If the circuitry you need requires leading-edge technology, that wafer will be expensive real estate for hosting relatively large MEMS structures. In such a case, you’re better off sticking with the expensive wafer for the circuits that need them and cheaper wafers for the MEMS structures that don’t.

There are also alternatives to wire-bonding MEMS and CMOS next to each other that stop short of monolithic integration. You can use flip-chip or TSVs in a 3D configuration or even bond entire wafers together, dicing afterwards. These approaches are often marketed as CMOS MEMS even though they’re not monolithic.

Each technique has its place, depending on the application, the amount of needed interconnect, the pad or bump pitch, and other considerations. Where integration into a single die is particularly advantageous is when there are lots of I/Os to interconnect – a feature particularly associated with arrays of items. TI’s DMD micro-mirror technology is a good example. Having each mirror’s driving circuit right under the mirror is really the only practical way to solve the problem, and that requires a single integrated chip.

There are three fundamental ways of integrating CMOS and MEMS: CMOS first, CMOS last, or “intra-CMOS.” The idea here is that you have a CMOS process “module” and a MEMS process module, and one comes before or after the other, or you can split the MEMS module, doing some before and some after the CMOS module. It’s generally recommended not to break up the CMOS module so that it can be done in standard commercial CMOS foundries without altering the process. The CMOS and MEMS modules are typically done in separate foundries.

A benefit of of doing CMOS last is that you get better predictability of the electrical behavior without having to limit the MEMS process steps. If you’re going to do the CMOS first, then you can’t allow the subsequent MEMS steps to contaminate the silicon or change the substrate stresses or doping profiles or start your metals flowing.

Despite that significant limitation, the consensus seems to be forming towards CMOS first because you can actually place the MEMS structures physically above the circuitry, reducing area significantly. That caps the MEMS operation temperatures at around 450 °C and limits any annealing processes to remove residual stresses.

Imec has a CMOS MEMS program, and they recommend CMOS first. According to imec’s Ann Witvrouw, they have found that, instead of using aluminum for freestanding structures (which has suboptimal mechanical properties) or poly-silicon (which has to be deposited at too hot a temperature), poly-SiGe has good physical properties, deposits at an acceptable temperature, and has the desired stress and stress gradient after deposition, meaning no annealing is required.

Even with CMOS first, there are two possibilities. One is to make the CMOS and MEMS bits next to each other, creating a cavity for the MEMS structure during the CMOS steps and filling it in with a sacrificial fill (like the sand in the pool). After the CMOS is complete, you can build the MEMS structure in the cavity. This keeps the CMOS and MEMS apart, which uses more area, but also makes it easier to access either for debug.

A more popular alternative is to finish the CMOS, passivate it, protecting it from subsequent chemicals, and then build the MEMS bits over it using additional layers. Not only does this save space, but it makes it easier to change the circuitry underneath (the next generation, for example) while keeping the mechanical structures intact.

A couple other companies, Akustica and Baolab, are going in a different direction by building the MEMS structures entirely out of the CMOS process layers, with no extra processing required whatsoever. This, of course, means having CMOS and MEMS side by side, but the benefit is that you can build the entire thing in a high-volume CMOS fab instead of having the CMOS foundry do the first part and then transferring the wafers to a MEMS foundry for the remaining steps.

Creating fish and fowl

Mechanical engineers have their own design methodologies, typically involving finite element analysis of various mechanical properties like stress and thermal flow. Circuit designers use a completely different set of tools for logic and circuit simulation.

In the case where MEMS and CMOS are built separately and united in an assembly step, each of the designers can safely remain within his or her world using familiar tools. But when designing a single, monolithic CMOS MEMS wafer, these two have to come together to create a single set of masks that will contain both electrical and mechanical features. Typical mechanical tools can’t comprehend electrical design, and typical electrical tools can’t handle mechanical concepts. Early players in this arena have had to blaze their own trails.

There is, however, a set of tools from a company called Coventor that goes a long way towards uniting the mechanical and electrical worlds. In fact, their suite contains aspects of system, electrical, mechanical, and TCAD tools.

The basic MEMS design tool is called CoventorWare. This handles all of the standard finite element analysis that would be familiar to any mechanical designer.

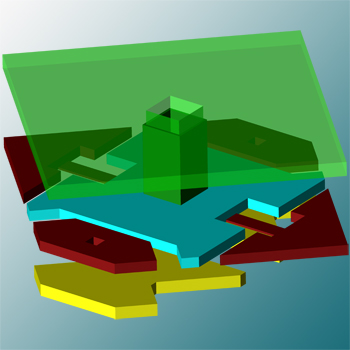

The MEMS+ tool allows system design including MEMS elements; this is where CMOS and MEMS come together. Within MEMS+, you can do 3D assembly and simulation of subsystems whose parameterized components come from a library. From this, you can generate a symbol for insertion into the circuit design, a netlist for simulation, and pcells for layout. You can even interface with Matlab for algorithmic design. So, with a single reference, you can scale a wide range of levels of abstraction.

Their other tool is called SEMulator3D: it lets you visualize the entire process stack to study how the manufacturing steps will work and how various components might affect each other. What you see on screen is like a virtual SEM of the component you’re studying. They handle the entire process, whether CMOS first or last or in between, and all components, whether electrical or mechanical, including DRAM and Flash memory cells.

They’re tightly integrated with Cadence Virtuoso, but they can work with tools from all of the Big 3 to get to mask. For the most part, it lets the CMOS and MEMS components coexist smoothly throughout the flow, although proprietary tricks are sometimes needed to navigate the DRC portion of the flow.

The fishermen and coop-keepers

We’ll finish off our marathon whirlwind tour by reviewing some of the participants in the CMOS MEMS arena. This review is necessarily succinct and was not assembled by looking up some listing, since I have found no such list. It’s cobbled together by following threads and web links and checking brochures and occasionally emailing for clarification; it may be incomplete. Note that this list doesn’t include pure MEMS companies or foundries.

One of the first successful high-volume CMOS MEMS producers, with accelerometers for airbag deployment. They also make gyroscopes, inertial measurement units (which combine multiple motion-sensing technologies), and microphones.

A fabless producer of microphones. They appear to make a distinction between “CMOS-compatible MEMS” and “CMOS MEMS,” the latter being how they describe a technology using only the CMOS layers. They claim to use CMOS MEMS as so defined.

Their NanoEMS technology uses only standard CMOS layers, requiring no separate MEMS steps. The only tweak to standard processes is a slight gas flow adjustment to change the refractive index of the passivation layer (which doesn’t require any re-qualification).Touted benefits are lower cost and smaller MEMS component features. They produce compasses, gyroscopes, accelerometers, inertial measurement units, and RF switches.

Fabless producer of MEMS IP suitable for integration with CMOS. They specialize in arrays of cavities containing one or more cantilevers. These can act as tunable capacitors or non-volatile memory (using “stiction” to maintain state).

A producer of oscillators for replacing quartz crystals. They use a separate foundry that they don’t identify; the foundry uses a CMOS-first process with the MEMS over the CMOS.

Doing fundamental CMOS MEMS research in Zurich, in particular for PZT RF switches, where the standard materials are a problem for CMOS. They also do custom cantilever work as well as lower-level nanotechnology research.

They have a proprietary Nasiri-Fabrication technique for bonding MEMS and CMOS wafers together in a manner they say reduces cost and is simpler than standard techniques. They make gyroscopes and accelerometers.

They have their own 8” MEMS line. They also have CMOS and bipolar lines, with wafer bonding capability. They produce, among other things, microphones, RF switches, pressure sensors, and flow sensors.

A foundry doing “integrated MEMS” via die- or wafer-level assembly of CMOS and MEMS components.

The other early high-volume CMOS MEMS producer, with arrays of digital mirrors used for displays. Each mirror lies above the circuitry needed to control mirror actuation.

A MEMS foundry that can do wafer bonding for CMOS MEMS. Their status was unclear, since the latest news on their website is from 2008. But they responded to my email, saying they are alive and well and have recently moved up to 8” MEMS capability.

TSMC, the biggest IC foundry, announced it was getting into MEMS in 2008. While not much information is available on their website, they confirmed that it’s full integrated CMOS MEMS using a CMOS-first process.

An IC foundry that announced just a couple months ago that it was launching its CMOS MEMS business. Information on their website is also scant, but, apparently, they’ve successfully made a microphone and an accelerometer for clients.

A monolithic CMOS MEMS foundry; it looks like they use a CMOS-first approach.

Other links:

Image courtesy Coventor.