Achronix Semiconductor Corporation is a fabless semiconductor corporation based in Santa Clara, California, offering high-end FPGA-based data acceleration solutions, designed to address high-performance, compute-intensive and real-time processing applications. Achronix is the only supplier to have both high-performance, high-density standalone FPGAs and licensed eFPGA IP solutions. Achronix Speedster®7t FPGA and Speedcore™ eFPGA IP offerings are further enhanced by ready-to-use VectorPath™ accelerator cards targeting AI, machine learning, networking and data center applications. All Achronix products are fully supported by the Achronix Tool Suite which enables customers to quickly develop their own custom applications.

Achronix has a global footprint, with sales and design teams across the U.S., Europe and Asia. For more information, please visit www.achronix.com.

Latest Featured Content from Achronix

featured video

ANIC Shell: Achronix Network Infrastructure Code

In anticipation of our demo at SmartNICs Summit 2023, here's a demo overview into Achronix's Ethernet network shell (ANIC) - a full ethernet data path built on top of the Speedster7t FPGA from data receive to data transmit at speeds up to 400G. In this video, we introduce the Achronix ANIC Networking Shell, a modular Ethernet SmartNIC that provides customers with a fully functional Ethernet datapath built on the Achronix SpeedsterAC7t1500 FPGA. The ANIC provides modular components such as Packet Engine, FIFO Buffer, Header/Parser, Rules Engine, Flow Processor, and DMA Engine that customers can select to provide the optimal datapath for their SmartNIC solution. In addition, over 50% of the Speedster7t FPGA is available for accelerating a customer’s network applications. We cover each modular element and the Achronix 2D NoC, which accelerates data transfers across the FPGA and enables customers to significantly reduce their solution design time. Director of Product Marketing, Ron Renwick, showcases our Achronix Speedster7t and its features, flexibility, and secret sauce (2D Network-on-Chip) to enable high-performance network data acceleration.

Demo: PCIe Gen5 x16 Running on VectorPath Accelerator Card

Achronix engineers show how to link the VectorPath Accelerator Card with Speedster7t FPGA to a PCIe Gen5 x16 host and read/write to GDDR6 memory via the full-chip two-dimensional Network on Chip (NoC). The NoC routes data from any of the high-speed interfaces to the core fabric within the FPGA at 2GHz without consuming any of the FPGA logic resources.

featured video

PCIe Gen5 x16 Running on the Achronix VectorPath Accelerator Card

In this demo, Achronix engineers show the VectorPath Accelerator Card successfully linking up to a PCIe Gen5 x16 host and write data to and read data from GDDR6 memory. The VectorPath accelerator card featuring the Speedster7t FPGA is one of the first FPGAs that can natively support this interface within its PCIe subsystem. Speedster7t FPGAs offer a revolutionary new architecture that Achronix developed to address the highest performance data acceleration challenges.

featured video

Demo: Achronix Speedster7t 2D NoC vs. Traditional FPGA Routing

This demonstration compares an FPGA design utilizing Achronix Speedster7t 2D Network on Chip (NoC) for routing signals with the FPGA device, versus using traditional FPGA routing. The 2D NoC provides a 40% reduction in logic resources required with 40% less compile time needed versus using traditional FPGA routing. Speedster7t FPGAs are optimized for high-bandwidth workloads and eliminate the performance bottlenecks associated with traditional FPGAs.

featured video

Achronix VectorPath Accelerator Card Uses PCIe Gen4 x16 to Communicate with AMD Ryzen PC

In this demonstration, the Achronix VectorPath™ accelerator card connects to an AMD Ryzen based PC using PCIe Gen4 x16 interface. The host PC issues commands to have the Speedster™7t FPGA on the VectorPath accelerator card write and read to external GDDR6 memory on the board. These data transactions are performed using the Speedster7t FPGA’s 2D network on chip or NoC which eliminates the need to write complex RTL code to design the host PC to GDDR6 memory interface.

featured paper

Watch PCIe Gen5 Interface Demo Running on a Speedster®7t FPGA from Achronix

PCIe Gen5 is the most advanced PCIe specification available today, providing data link capable of a 32 GT/s for next-generation systems. You can start to design your PCIe Gen5 system today using the Achronix Speedster7t FPGA. This demonstration shows a successful PCIe Gen5 link between a Lecroy PCIe exerciser and a Speedster7t FPGA. The Speedster7t family is one of the first FPGAs available now that natively supports the PCIe Gen5 specification.

featured video

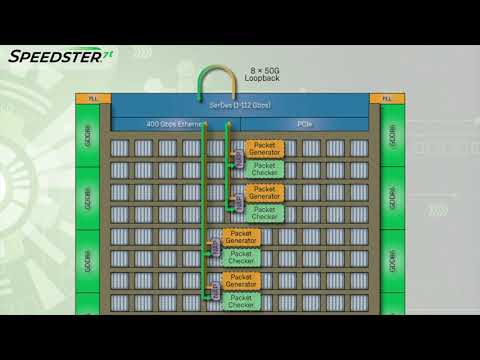

See 400 GbE Running on a Speedster®7t FPGA from Achronix

400GbE is required for next-generation, high-performance networking applications. In this video, Achronix demonstrates 400GbE connectivity on a Speedster7t FPGA integrated into a VectorPath™ PCIe accelerator card. The demonstration shows 400GbE traffic generated within the FPGA and transmitted across the FPGA’s 2D network on chip or NoC to the Ethernet subsystem. The 400GbE traffic is then looped back and checked within the FPGA fabric to compare to the original data stream.

featured paper

An FPGA-Based Solution for a Graph Neural Network Accelerator

Graph Neural Networks (GNN) drive high demand for compute and memory performance and a software only based implementation of a GNN does not meet performance targets. As a result, there is an urgent need for hardware-based GNN acceleration. While traditional convolutional neural network (CNN) hardware acceleration has many solutions, the hardware acceleration of GNN has not been fully discussed and researched. This white paper reviews the latest GNN algorithms, the current status of acceleration technology research, and discusses FPGA-based GNN acceleration technology.

Chalk Talks Featuring Achronix

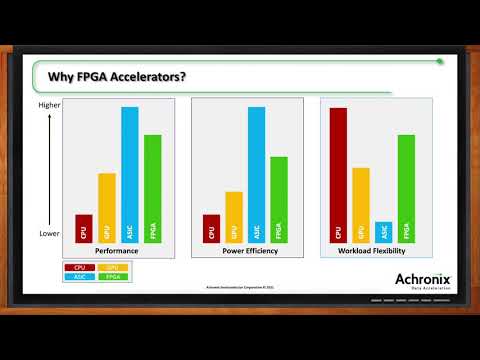

FPGAs Advance Data Acceleration in the Digital Transformation Age

Acceleration is becoming a critical technology for today’s data-intensive world. Conventional processors cannot keep up with the demands of AI and other performance-intensive workloads, and engineering teams are looking to acceleration technologies for leverage against the deluge of data. In this episode of Chalk Talk, Amelia Dalton chats with Tom Spencer of Achronix about the current revolution in acceleration technology, and about specific solutions from Achronix that take advantage of leading-edge FPGAs, design IP, and even plug-and-play accelerator cards to address a wide range of challenges.

Benefits of FPGAs & eFPGA IP in Futureproofing Compute Acceleration

In the quest to accelerate and optimize today’s computing challenges such as AI inference, our system designs have to be flexible above all else. At the confluence of speed and flexibility are today’s new FPGAs and e-FPGA IP. In this episode of Chalk Talk, Amelia Dalton chats with Mike Fitton from Achronix about how to design systems to be both fast and future-proof using FPGA and e-FPGA technology.